| Back to Main Page |

|

|

|

|

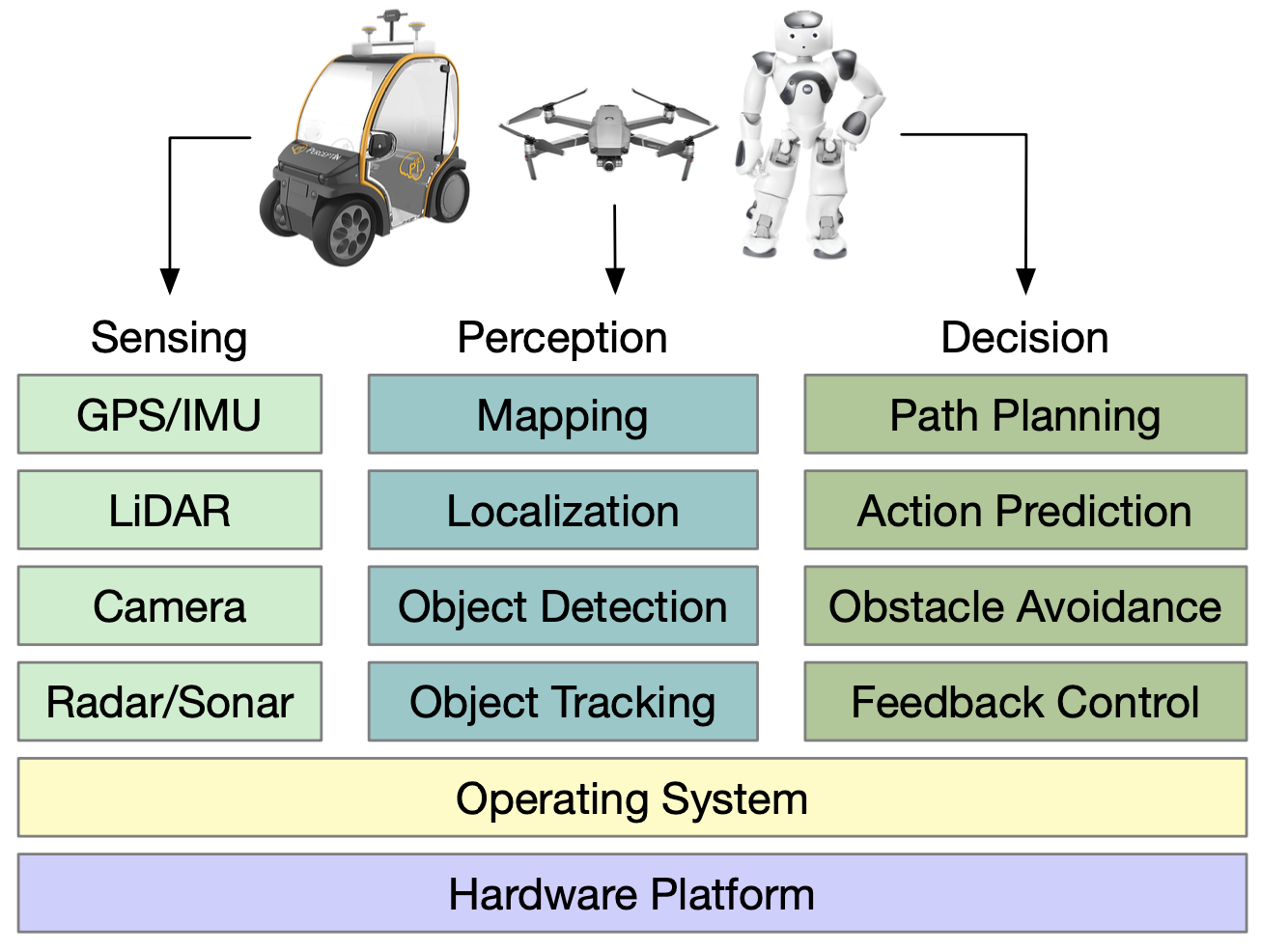

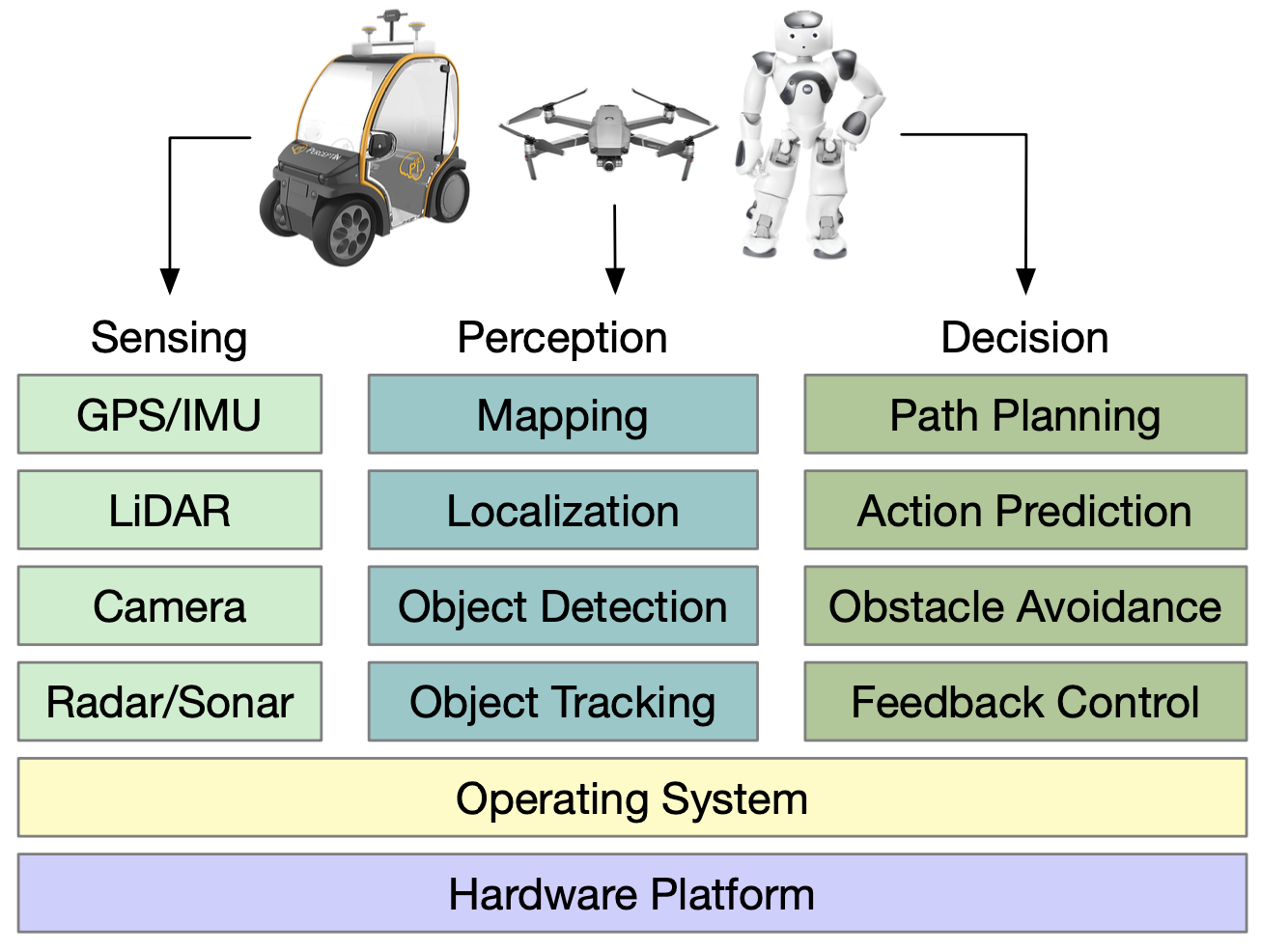

Shaoshan Liu, Zishen Wan, Bo Yu, Yu Wang Editor: Natalie Enright Jerger Synthesis Lectures on Computer Architecture (Morgan & Claypool Publishers), pp.1-218, Jun 2021 Book This book provides a thorough overview of the state-of-the-art FPGA-based robotic computing accelerator designs and summarizes their adopted optimized techniques. This book consists of ten chapters, delving into the details of how FPGAs have been utilized in robotic perception, localization, planning, and multi-robot collaboration tasks. In addition to individual robotic tasks, this book provides detailed descriptions of how FPGAs have been used in robotic products, including commercial autonomous vehicles and space exploration robots. Some key observations of this book has been published as a survey paper in IEEE Circuits and Systems Magazine, 2021. |

|

Yiming Gan, Bo Yu, Zishen Wan, Shaoshan Liu Publishing House of Electronics Industry, pp.1-224, Nov 2024 Book (In Chinese) This book provides a comprehensive overview of state-of-the-art embodied AI robotic systems, advancing toward artificial general intelligence. It comprises 14 chapters. Part 1 (chapters 1-2) introduces embodied AI robots background and recent developments. Part 2 (chapters 3-6) explores key systems for embodied robots, including perception, localization, planning, and control. Part 3 (chapters 7-9) deeps dive into LLMs for robotic frameworks. Part 4 (chapters 10-13) discusses efficiency, robustness, safety, and data challenges in embodied AI, along with solutions. Part 5 (chapter 14) demonstrates embodied robotic applications. |

|

|

|

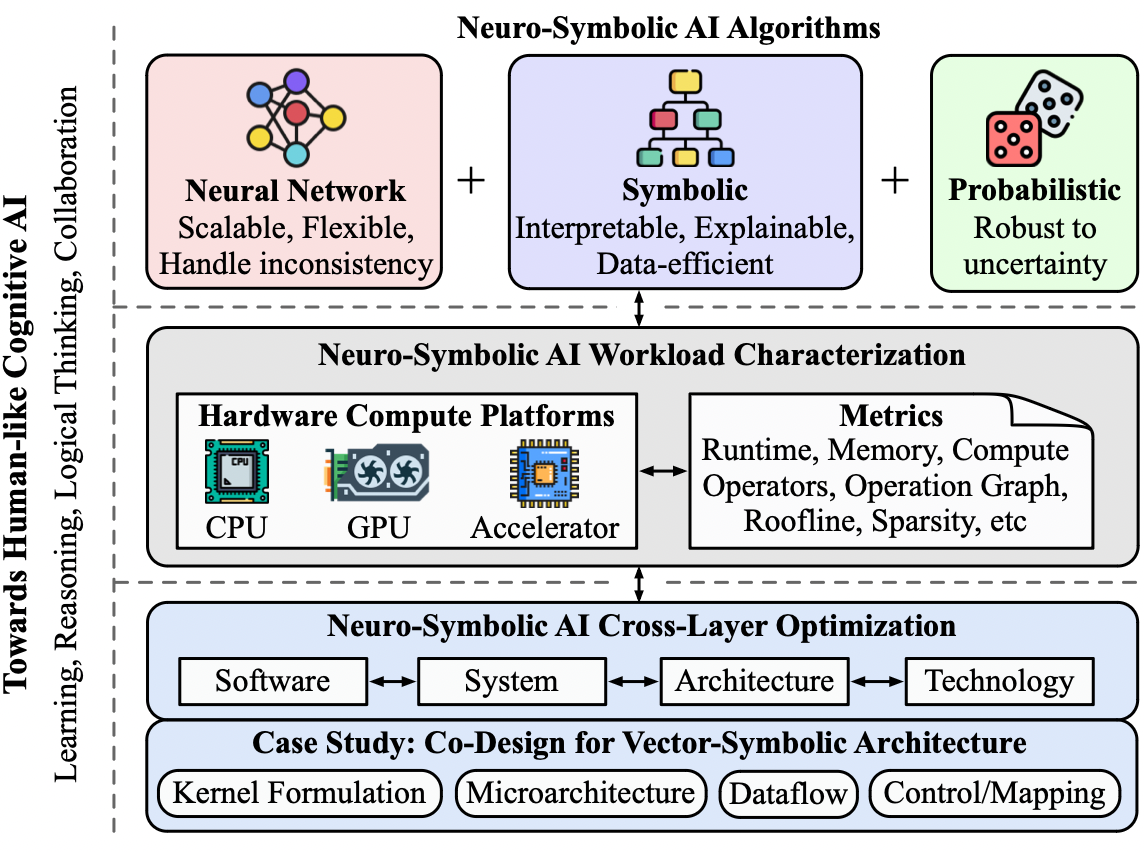

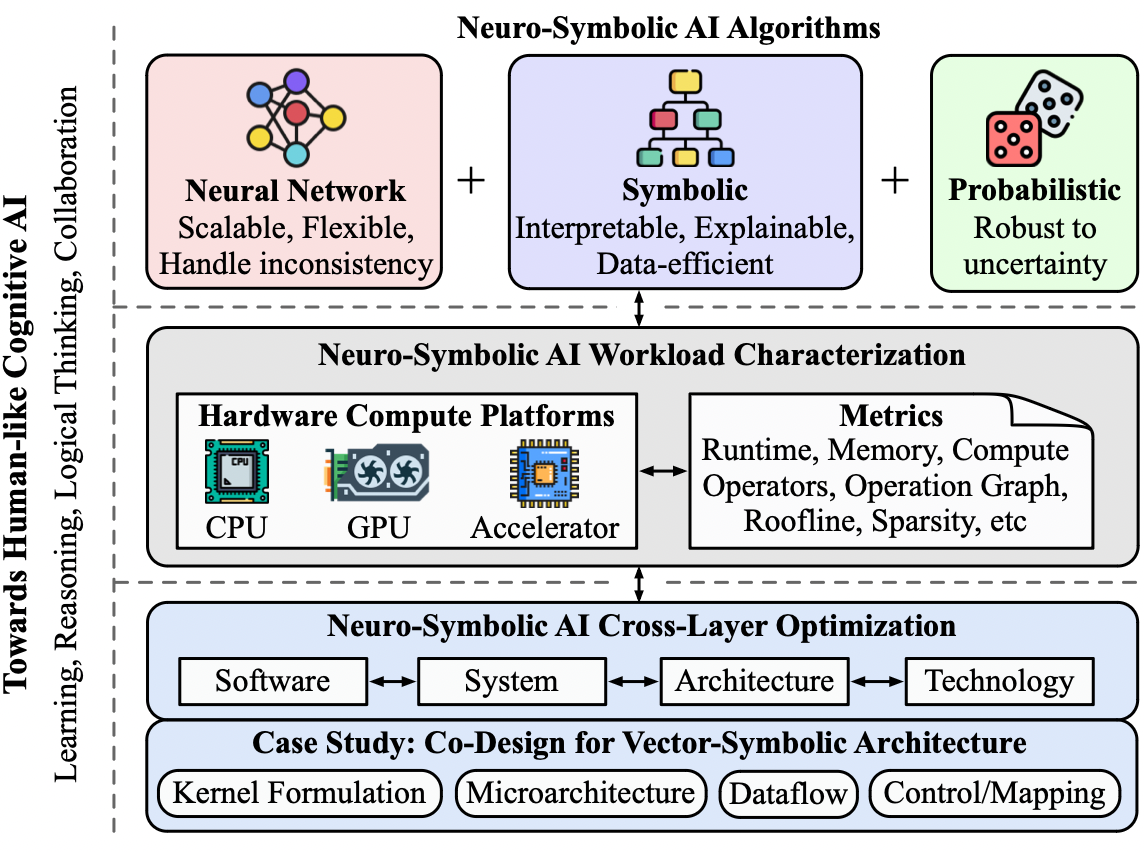

Zishen Wan, Vijay Janapa Reddi, Tushar Krishna, Arijit Raychowdhury Design Automation Conference (DAC) PhD Forum, 2025 First Place, ACM/IEEE DAC PhD Forum Poster / Media This poster presents tailored computing methodology for cross-layer software-system-hardware co-design to develop efficient, reliable, and adaptable architectures for embodied and neuro-symbolic intelligence. |

|

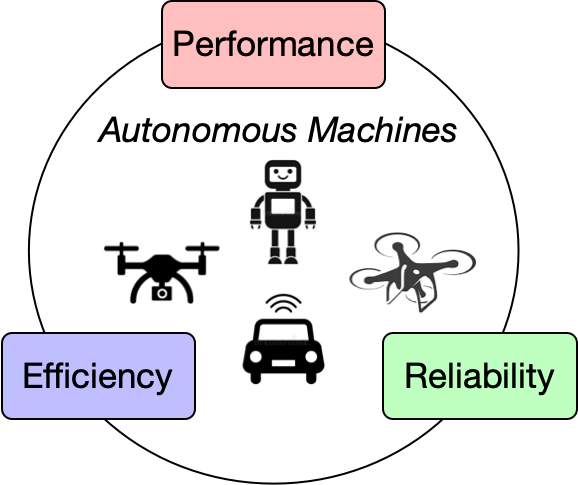

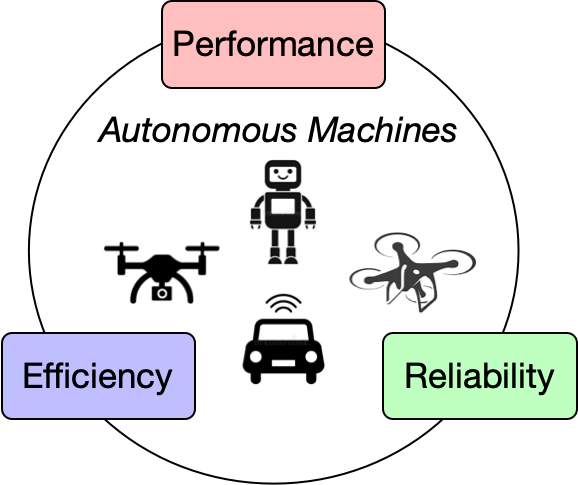

Zishen Wan, Vijay Janapa Reddi, Arijit Raychowdhury ACM Student Research Competition (SRC), Grand Final, 2023 First Place, ACM/SIGBED Student Research Competition (SRC) Paper / Slide / Media / Media This report summarizes our recent efforts in facilitating the development of scalable, efficient, adaptive, and reliable autonomous machine computing, including automatic domain-specific SoC exploration, software-hardware co-design, and performance-efficiency-resilience co-optimization. |

|

(Research Topics: Embodied AI Robotic System / Reliability of AMC / Hardware Architecture of AMC / Benchmarking and Design Flow of AMC) |

|

Embodied and Cognitive Agentic System Design |

|

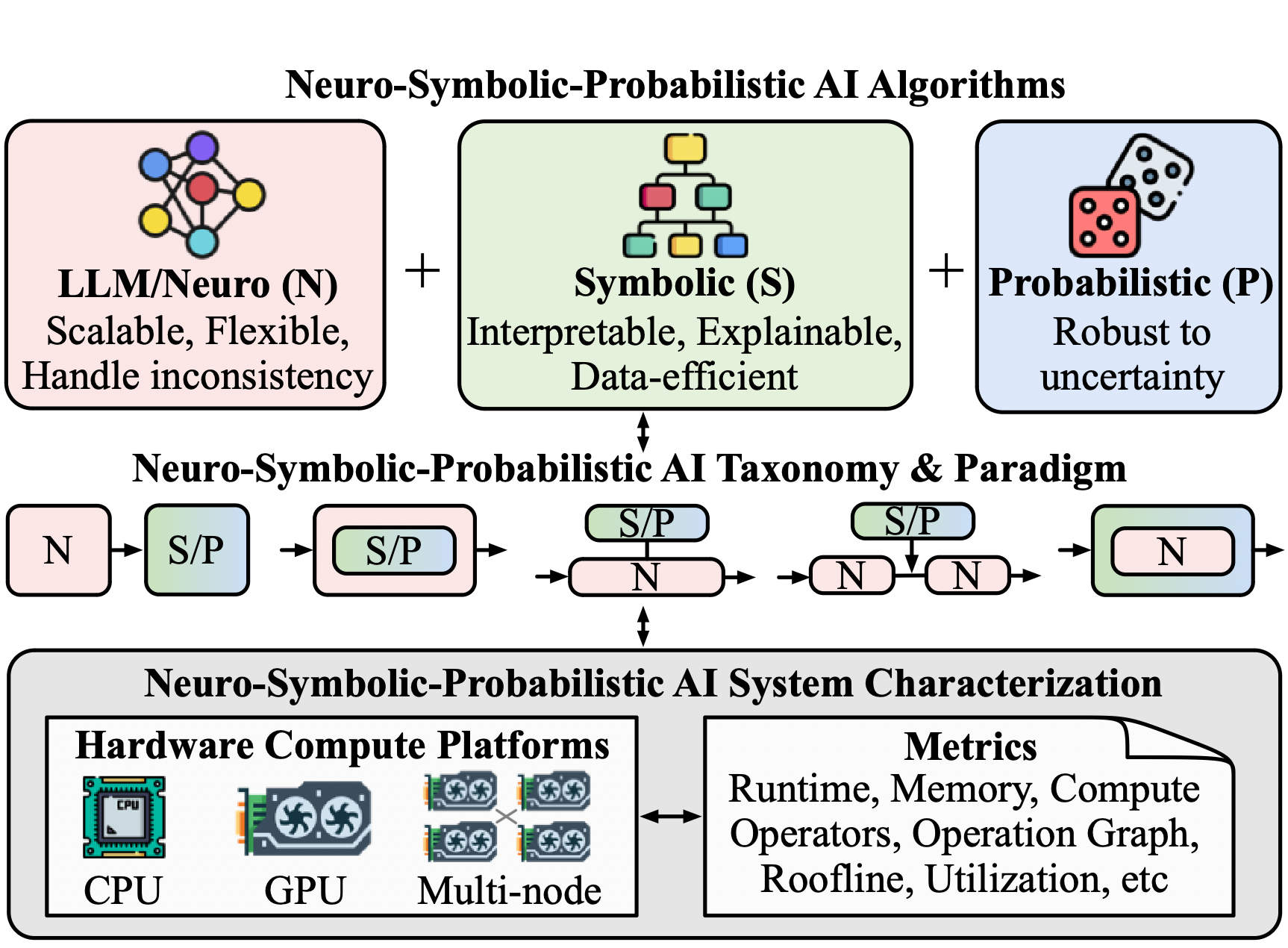

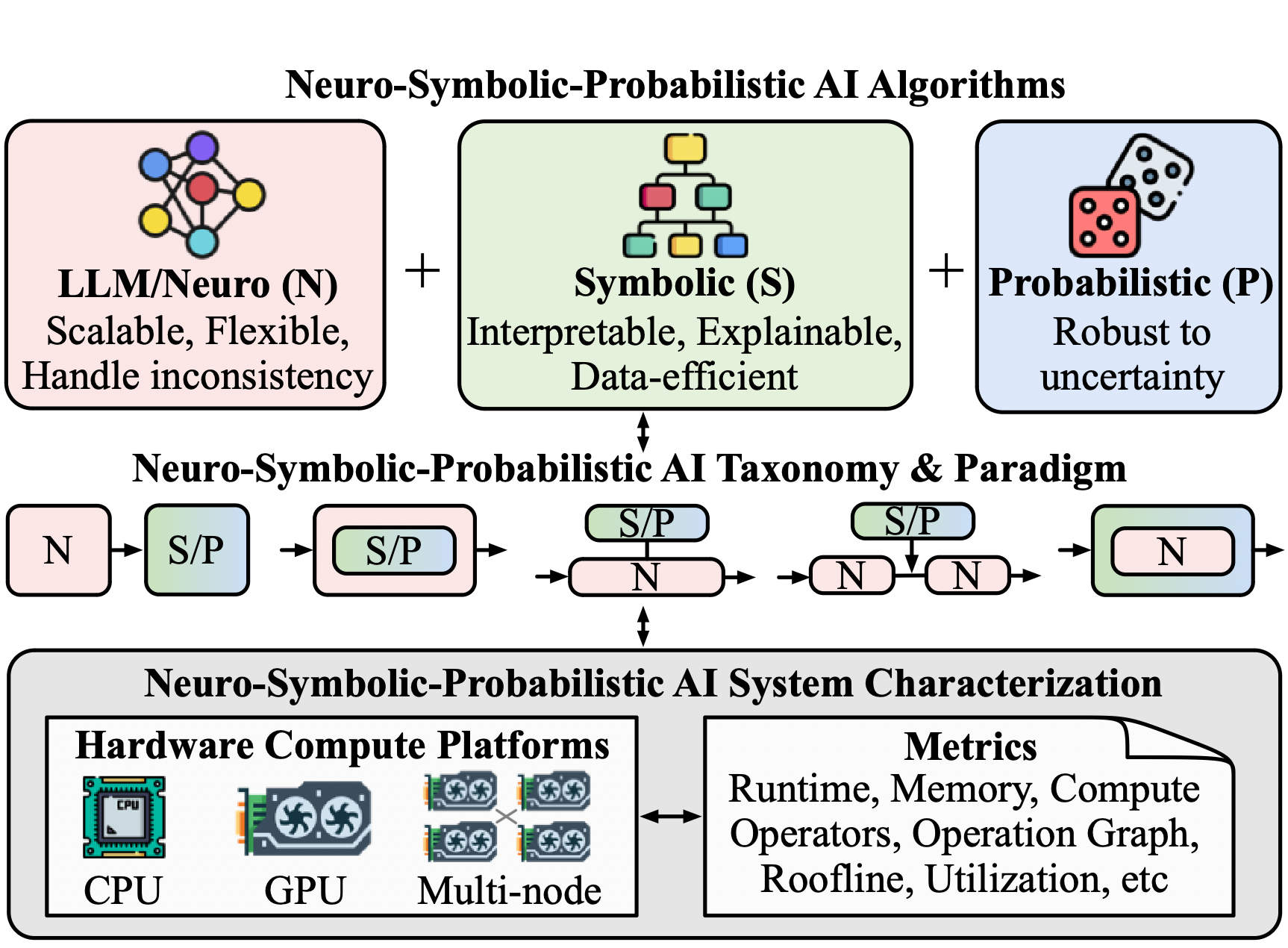

Zishen Wan, Hanchen Yang, Jiayi Qian, Ritik Raj, Joongun Park, Chenyu Wang, Arijit Raychowdhury, Tushar Krishna ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2026 Paper (To appear) Compositional AI integrates LLMs, symbolic, and probabilistic modules to enhance interpretability, robustness, and trustworthiness for cognitive applications. This paper presents a comprehensive system-level analysis of neuro-symbolic-probabilistic AI and reveals its key performance characteristics. |

|

Zishen Wan*, Hanchen Yang*, Ritik Raj*, Che-Kai Liu, Ananda Samajdar, Arijit Raychowdhury, Tushar Krishna International Symposium on High-Performance Computer Architecture (HPCA), 2025 Best Paper Award, DARPA SRC JUMP 2.0, 2024 Paper / Slide / Slide (long version) / Poster / Media We propose CogSys, a characterization and co-design framework dedicated to neurosymbolic AI system acceleration, aiming to win both reasoning efficiency and scalability. |

|

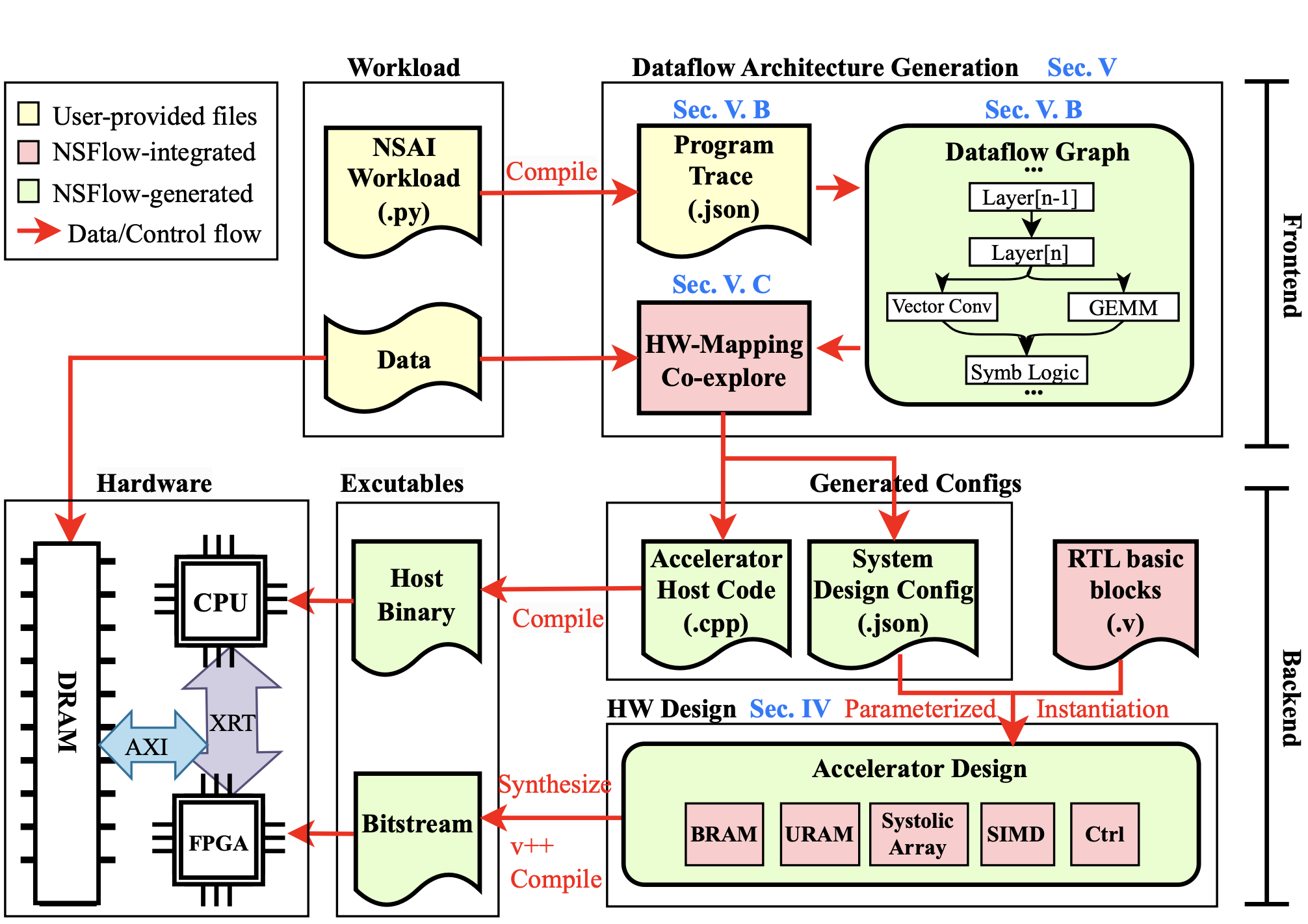

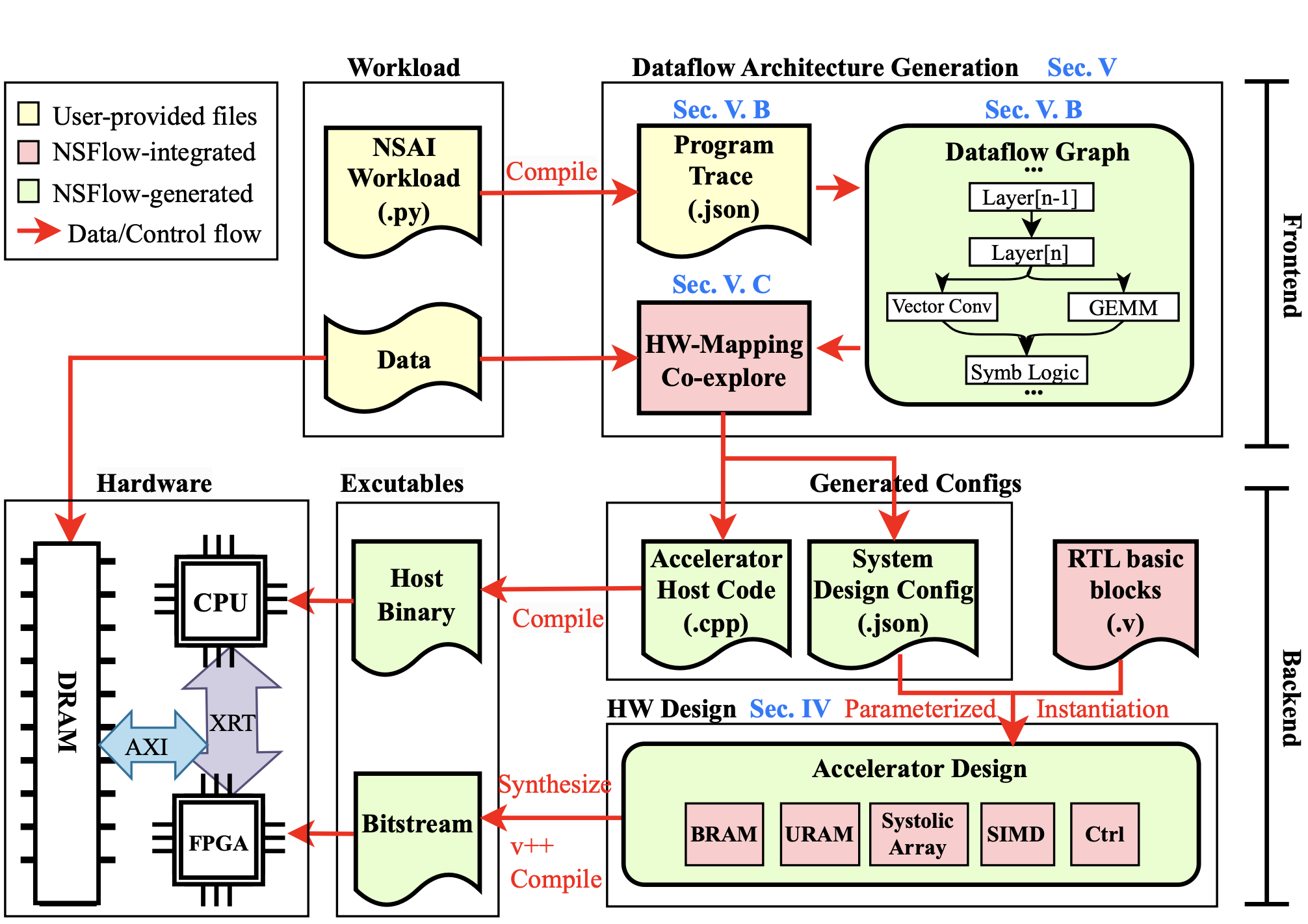

Hanchen Yang*, Zishen Wan*, Ritik Raj, Joongun Park, Ziwei Li, Ananda Samajdar, Arijit Raychowdhury, Tushar Krishna ACM/IEEE Design Automation Conference (DAC), 2025 Paper / Slide We propose NSFlow, an FPGA framework for efficient, scalable, and adaptive across neuro-symbolic systems. NSFlow features a design architecture generator that identifies workload data dependencies and creates dataflow architectures, as well as reconfigurable array with flexible compute units and re-organizable memory. |

|

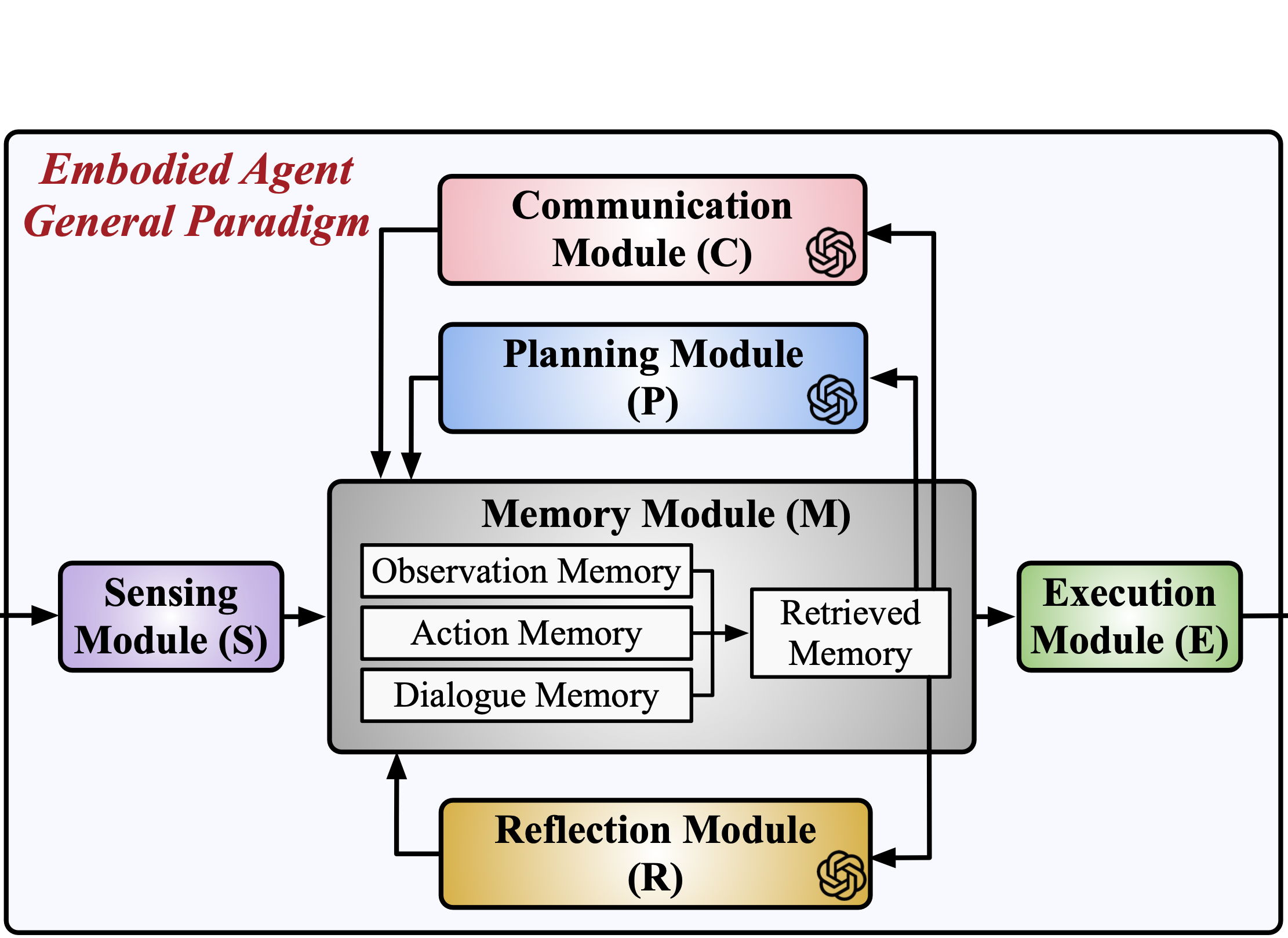

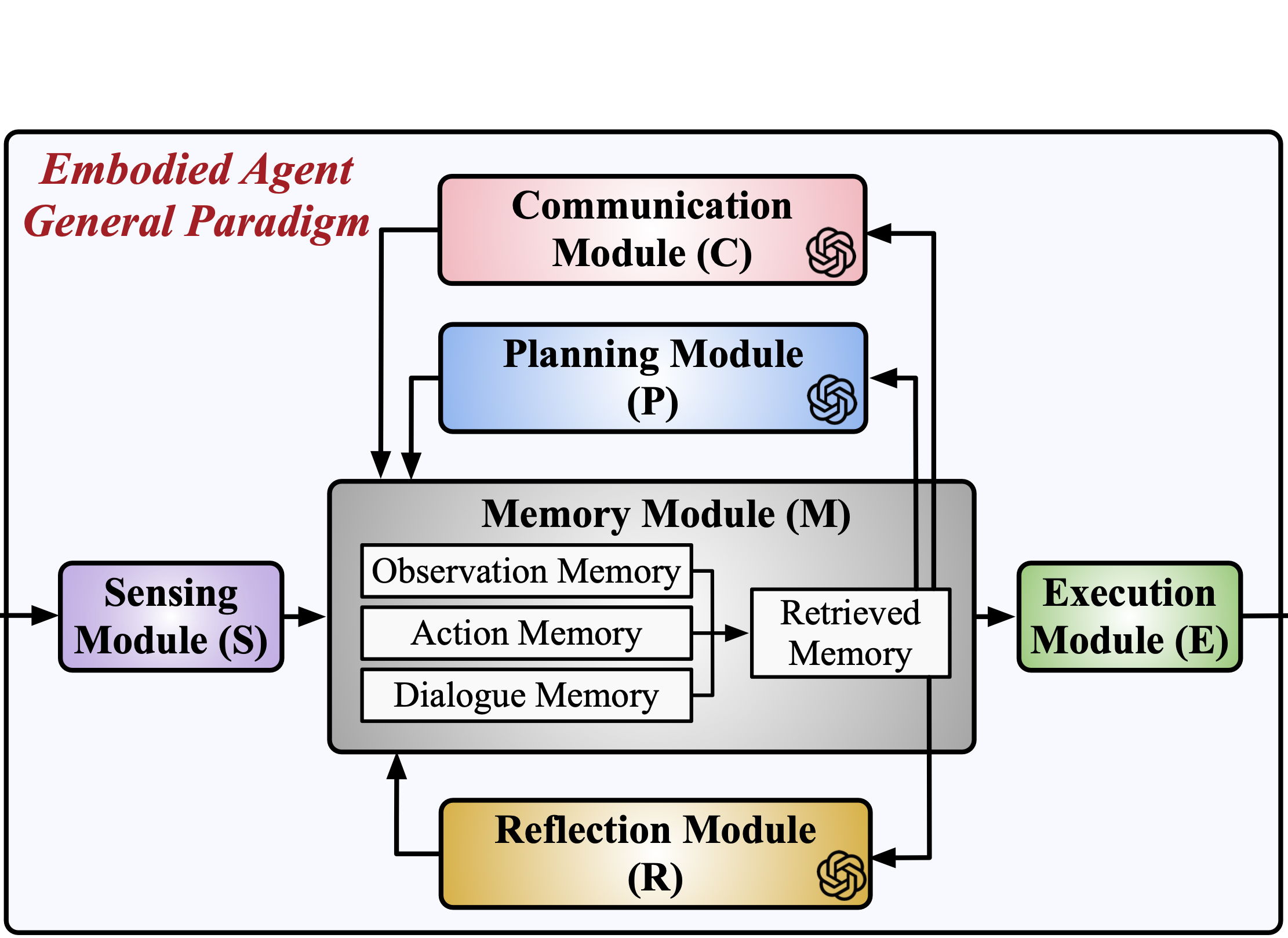

Zishen Wan, Jiayi Qian, Yuhang Du, Jason Jabbour, Yilun Du, Yang (Katie) Zhao, Arijit Raychowdhury, Tushar Krishna, Vijay Janapa Reddi IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2025 Paper This paper systematically categorizes the workload characteristics of embodied agent systems and presents a benchmark suite to evaluate their task performance and system efficiency, suggests system optimization strategies to improve the performance, efficiency, and scalability of future embodied system design. |

|

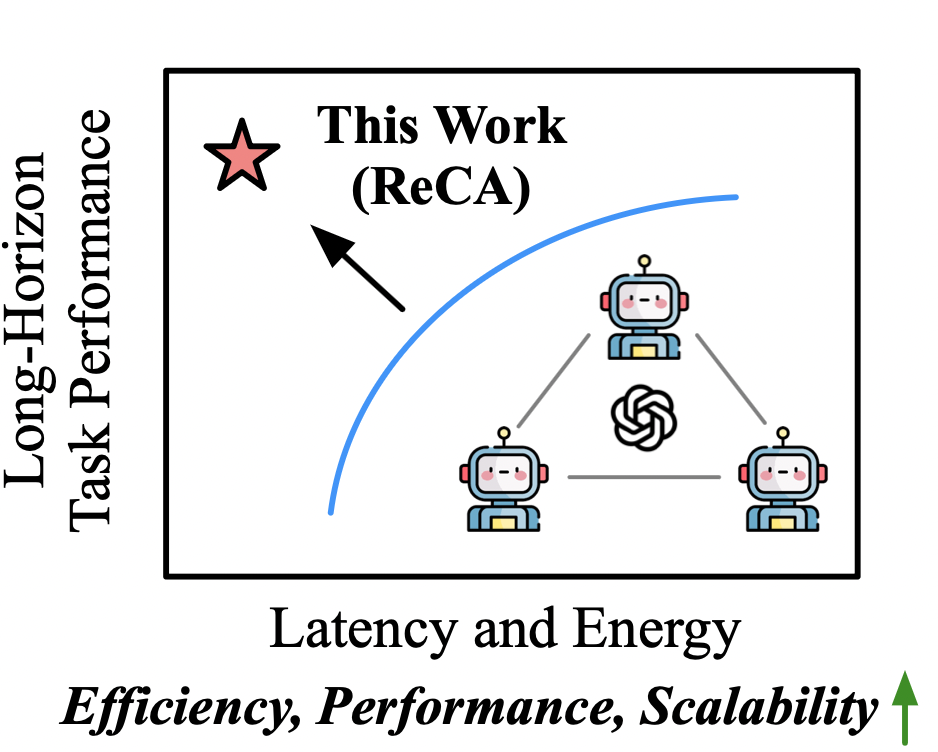

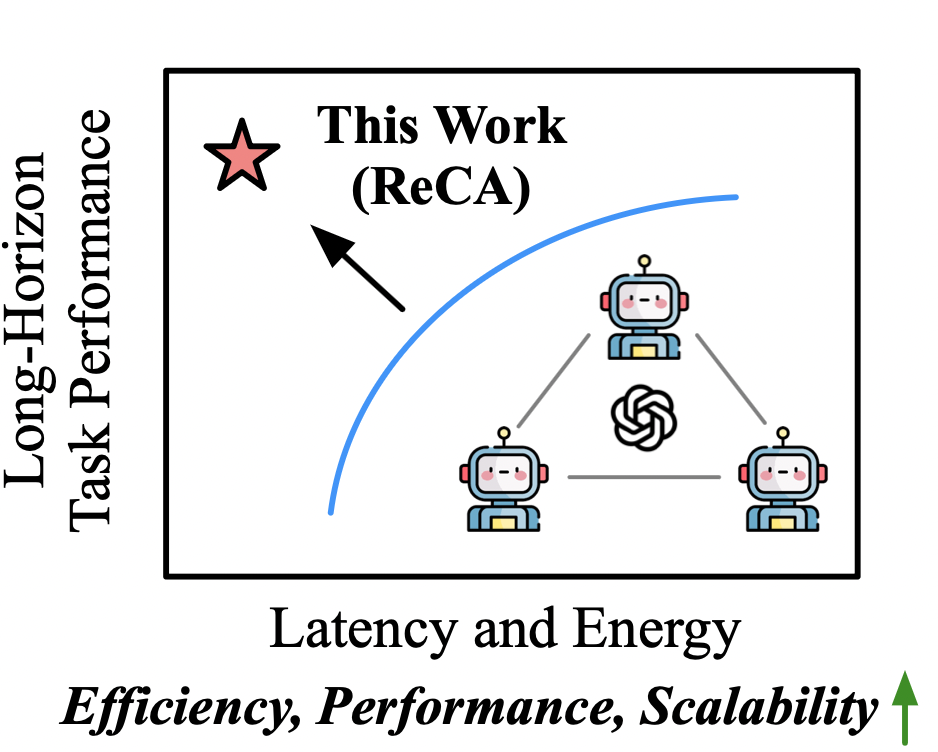

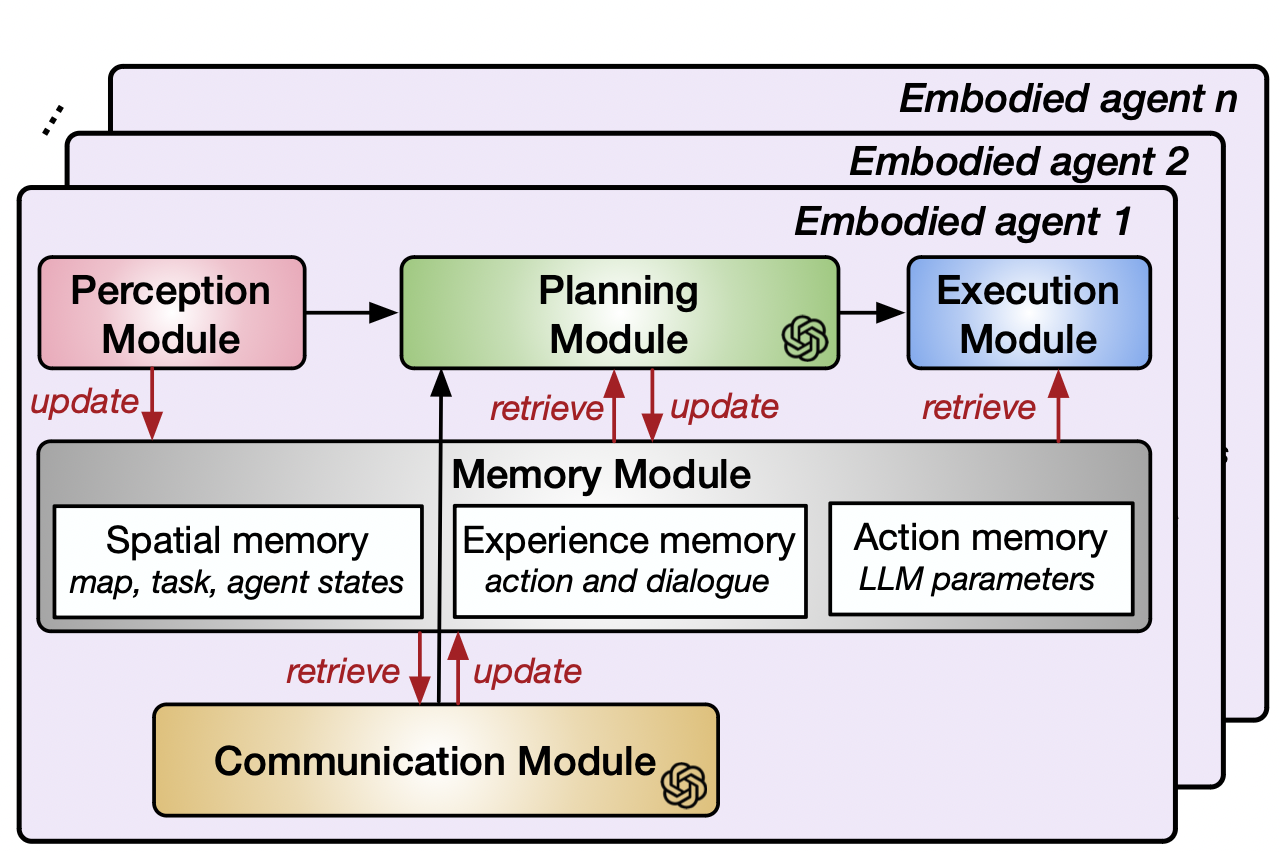

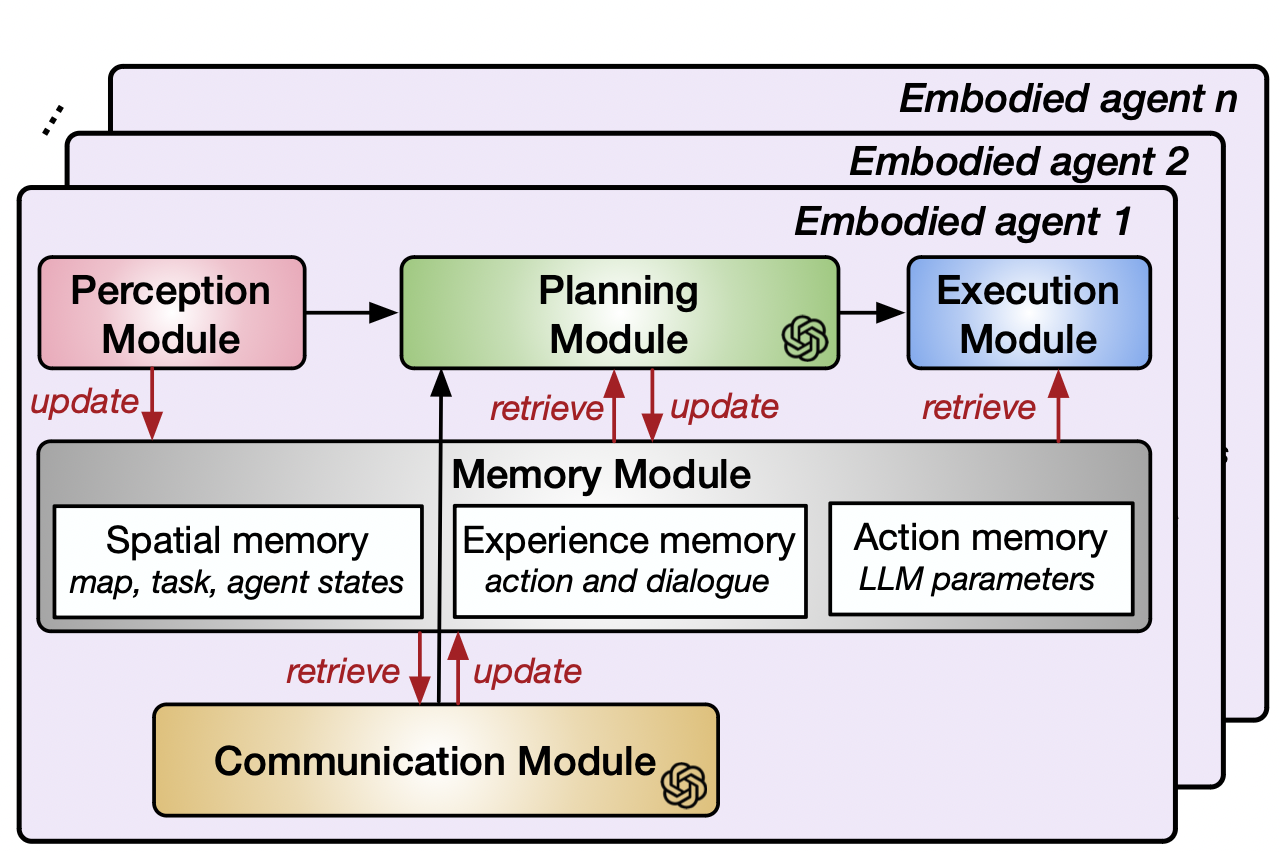

Zishen Wan, Yuhang Du, Mohamed Ibrahim, Jiayi Qian, Jason Jabbour, Yang (Katie) Zhao, Vijay Janapa Reddi, Tushar Krishna, Arijit Raychowdhury ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2025 Paper / Slide / Poster We propose ReCA, a characterization and system-architecture co-design framework dedicated to cooperative embodied AI agent system acceleration, aiming to enhance both long-horizon multi-objective planning task efficiency and system scalability. |

|

Zishen Wan, Yuhang Du, Mohamed Ibrahim, Yang (Katie) Zhao, Tushar Krishna, Arijit Raychowdhury ACM/IEEE International Conference on Computer-Aided Design (ICCAD), 2024 Paper We present a cognitive-inspired modular framework for cooperative embodied AI systems and identify the system inherent characteristics and optimization opportunities. Evaluated on long-horizon multi-objective tasks, our cross-layer optimization achieves an average 3.93x speedup in end-to-end task execution. |

|

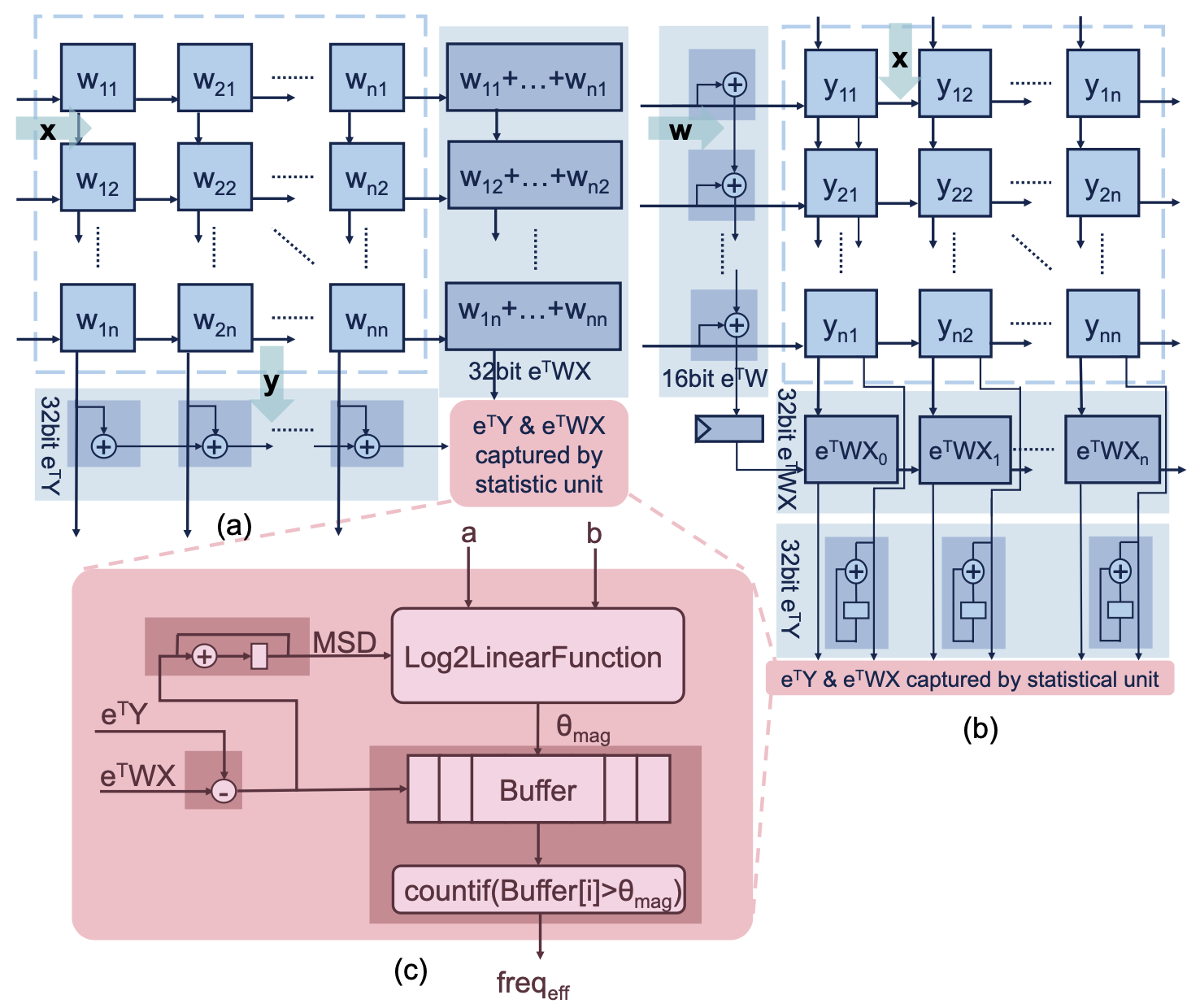

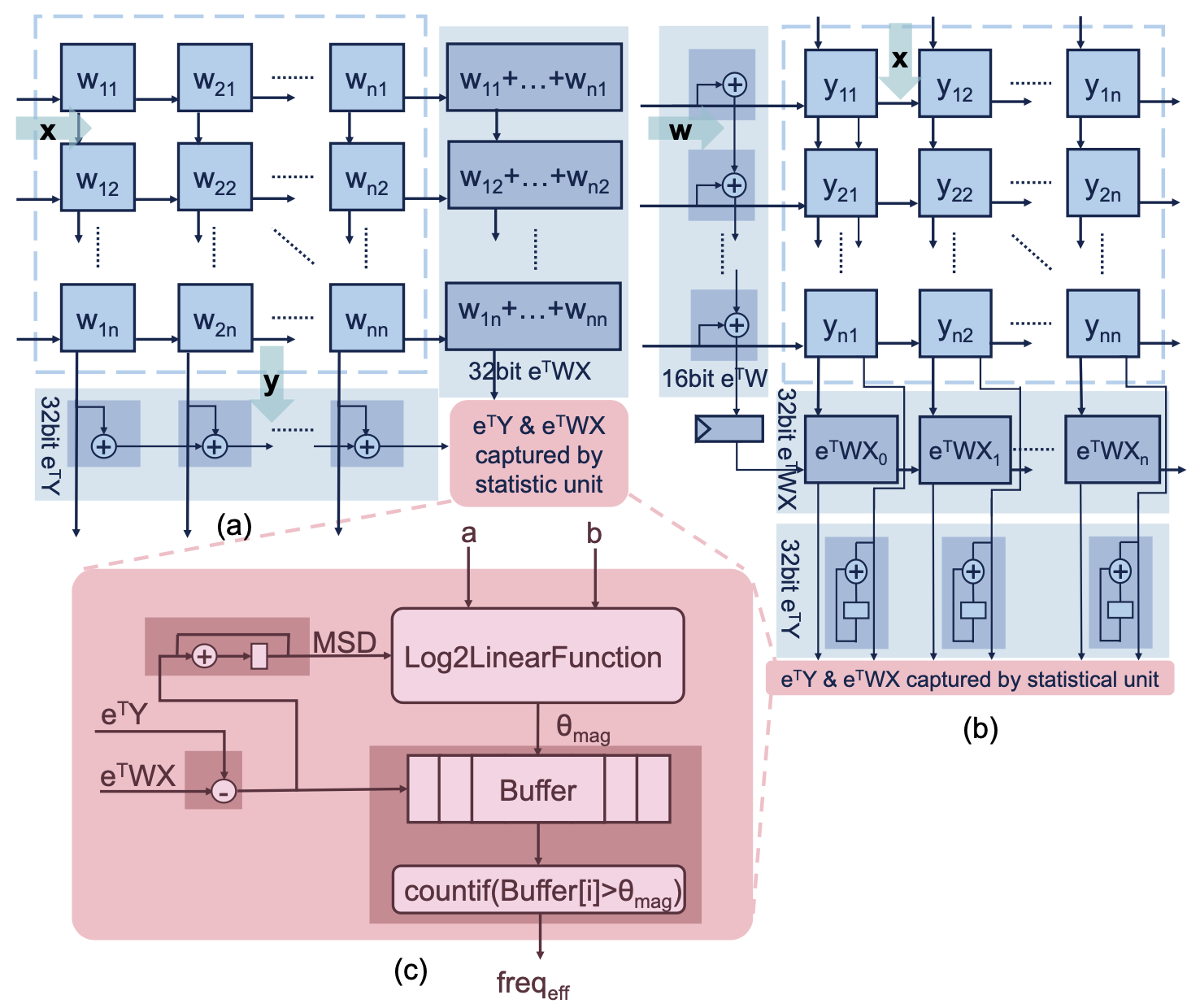

Zishen Wan, Che-Kai Liu, Hanchen Yang, Ritik Raj, Chaojian Li, Haoran You, Yonggan Fu, Cheng Wan, Sixu Li, Youbin Kim, Ananda Samajdar, Yingyan (Celine) Lin, Mohamed Ibrahim, Jan M. Rabaey, Tushar Krishna, Arijit Raychowdhury IEEE Transactions on Circuits and Systems for Artificial Intelligence (TCASAI), 2024 Paper / Slide / Fortune News / CoCoSys News We analyze the neuro-symbolic workload chracteristics, and present a hardware acceleration case study for vector-symbolic architecture to improve the performance, efficiency, and scalability of neuro-symbolic computing. |

|

Reliability of Autonomous Machine Computing |

|

Tong Xie, Jiawang Zhao, Zishen Wan, Zuodong Zhang, Yuan Wang, Runsheng Wang, Ru Huang, Meng Li ACM/IEEE Design Automation Conference (DAC), 2025 Paper We propose ReaLM, an algorithm/circuit co-design framework for resileint and efficient LLM inference. ReaLM systematically characterize the fault tolerance of LLMs, and introduces a statistical algorithm-based fault tolerance algorithm and error detection circuit to enable cost-effective fault detection and mitigation for LLMs. |

|

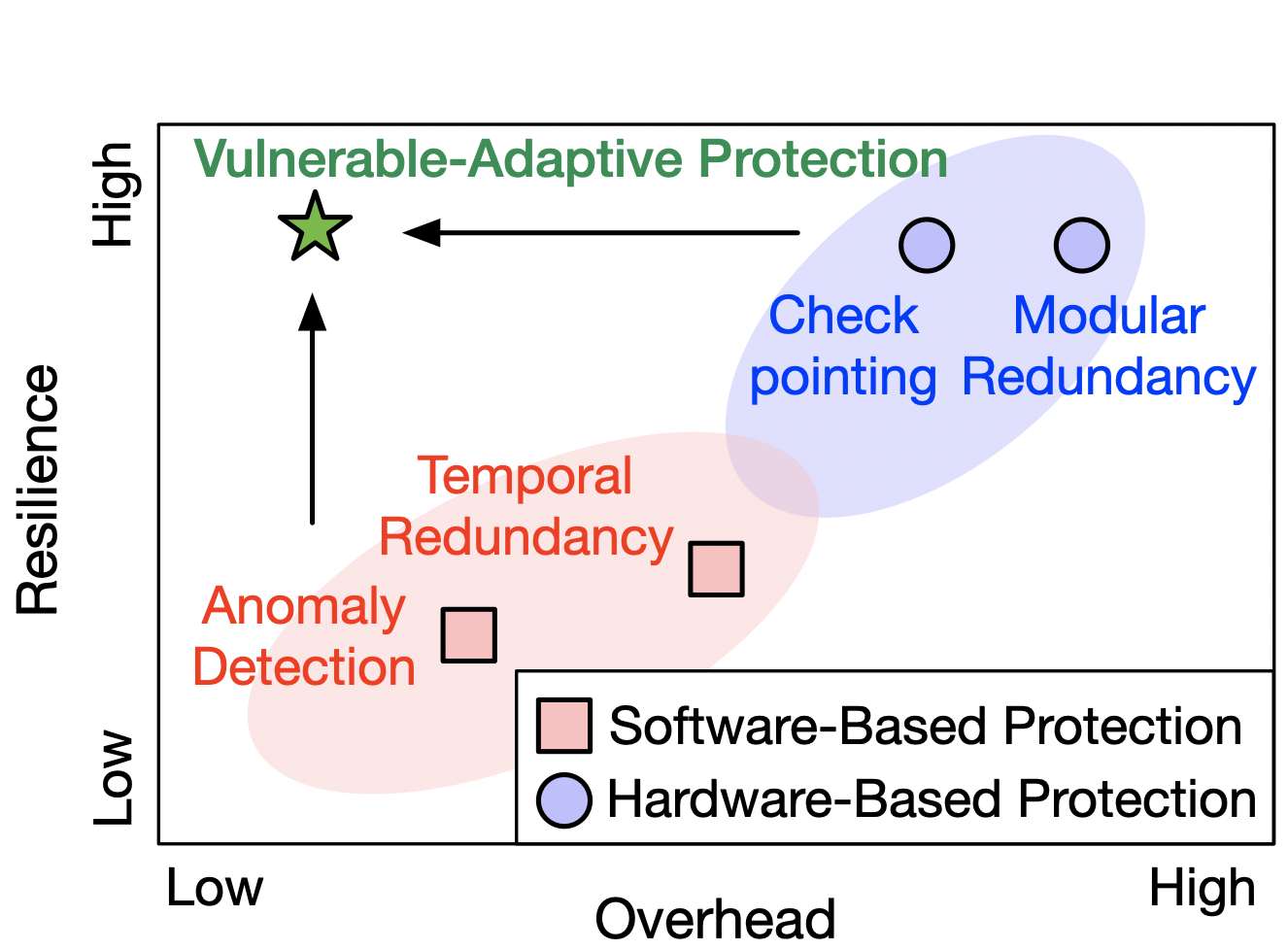

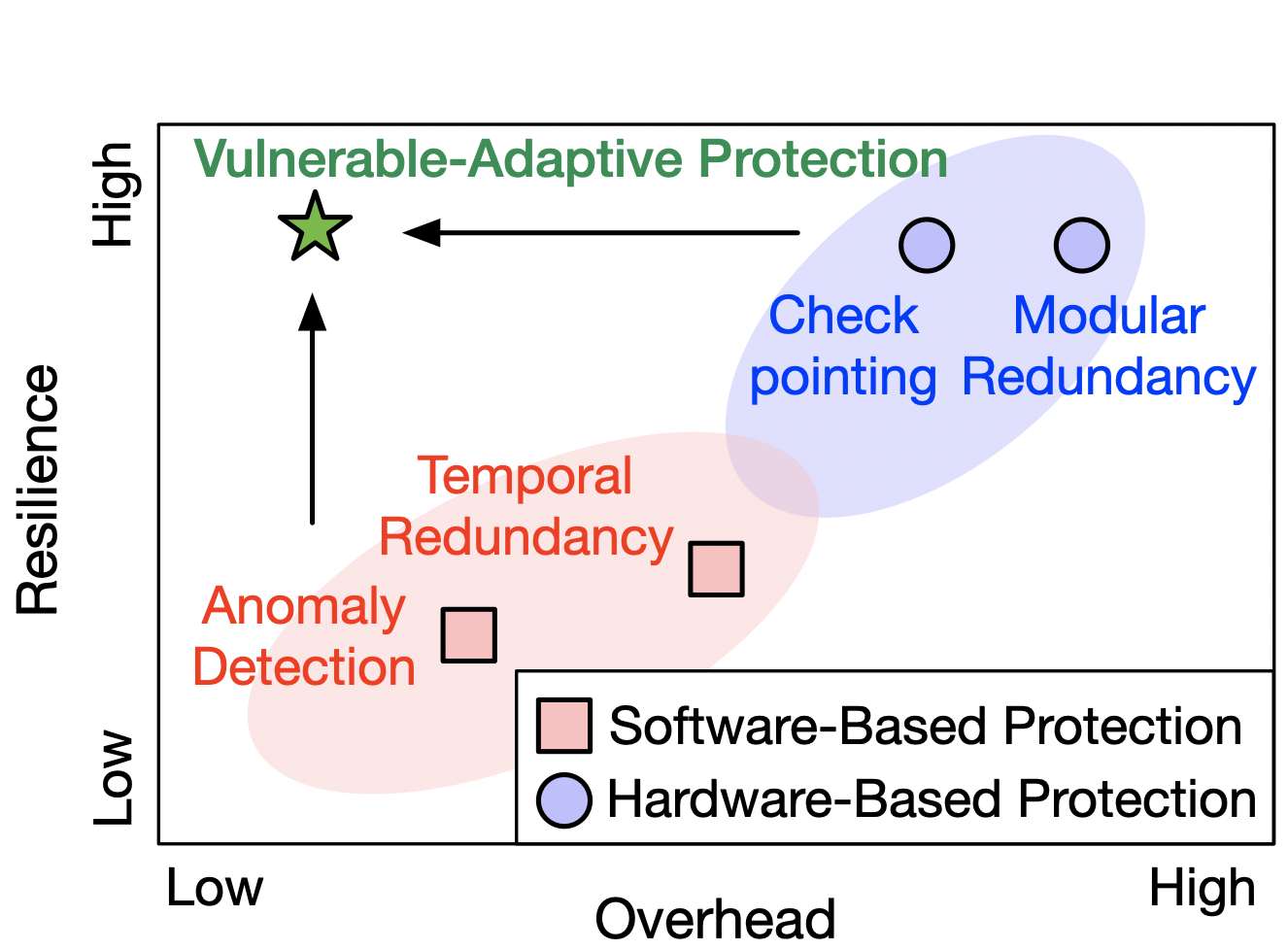

Zishen Wan*, Yiming Gan*, Bo Yu, Shaoshan Liu, Arijit Raychowdhury, Yuhao Zhu Communications of the ACM (CACM), 2024 Paper / Slide / ACM News / GT News / TechXplore News / MIT Technology Review News We characterize the inherent resilience of different compute kernels in autonomous vehicles and drones systems. We analyze the protection design landscape and propose the lightweight Vulnerable-Adaptive Protection (VAP) paradigm for resilient autonomous machines. |

|

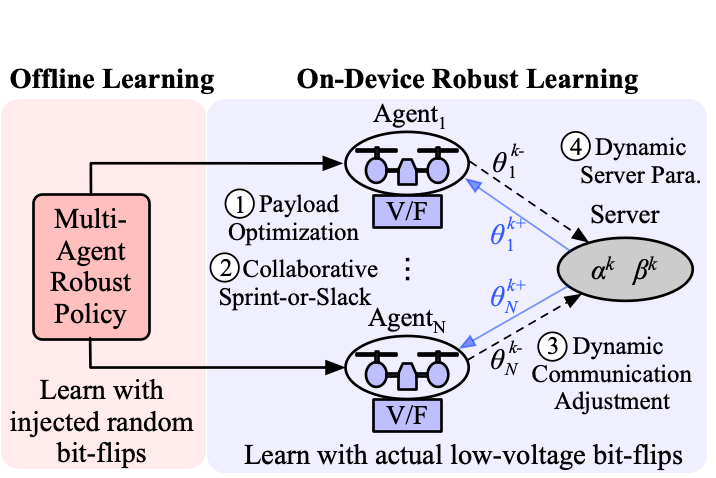

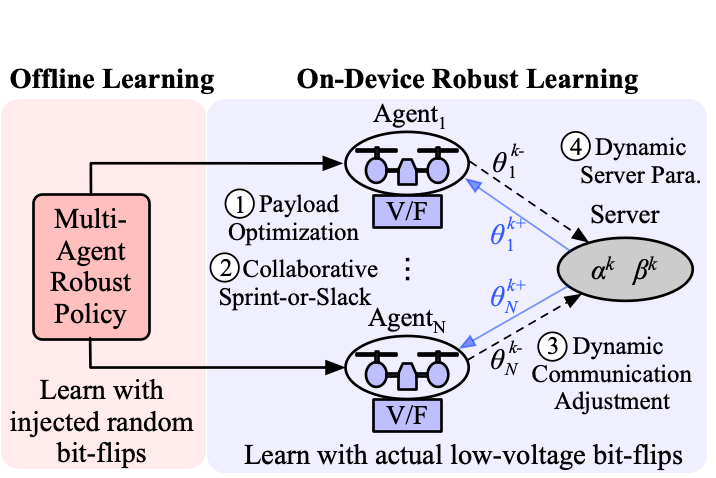

Zishen Wan, Nandhini Chandramoorthy, Karthik Swaminathan, Pin-Yu Chen, Kshitij Bhardwaj, Vijay Janapa Reddi, Arijit Raychowdhury ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2024 Best Poster Award, IBM IEEE AI Compute Symposium 2023 Paper / Slide / Poster / Lightning Talk / Media We propose MulBERRY, a multi-agent robust learning framework to enhance bit error robustness and energy efficiency for autonomous swarm systems. |

|

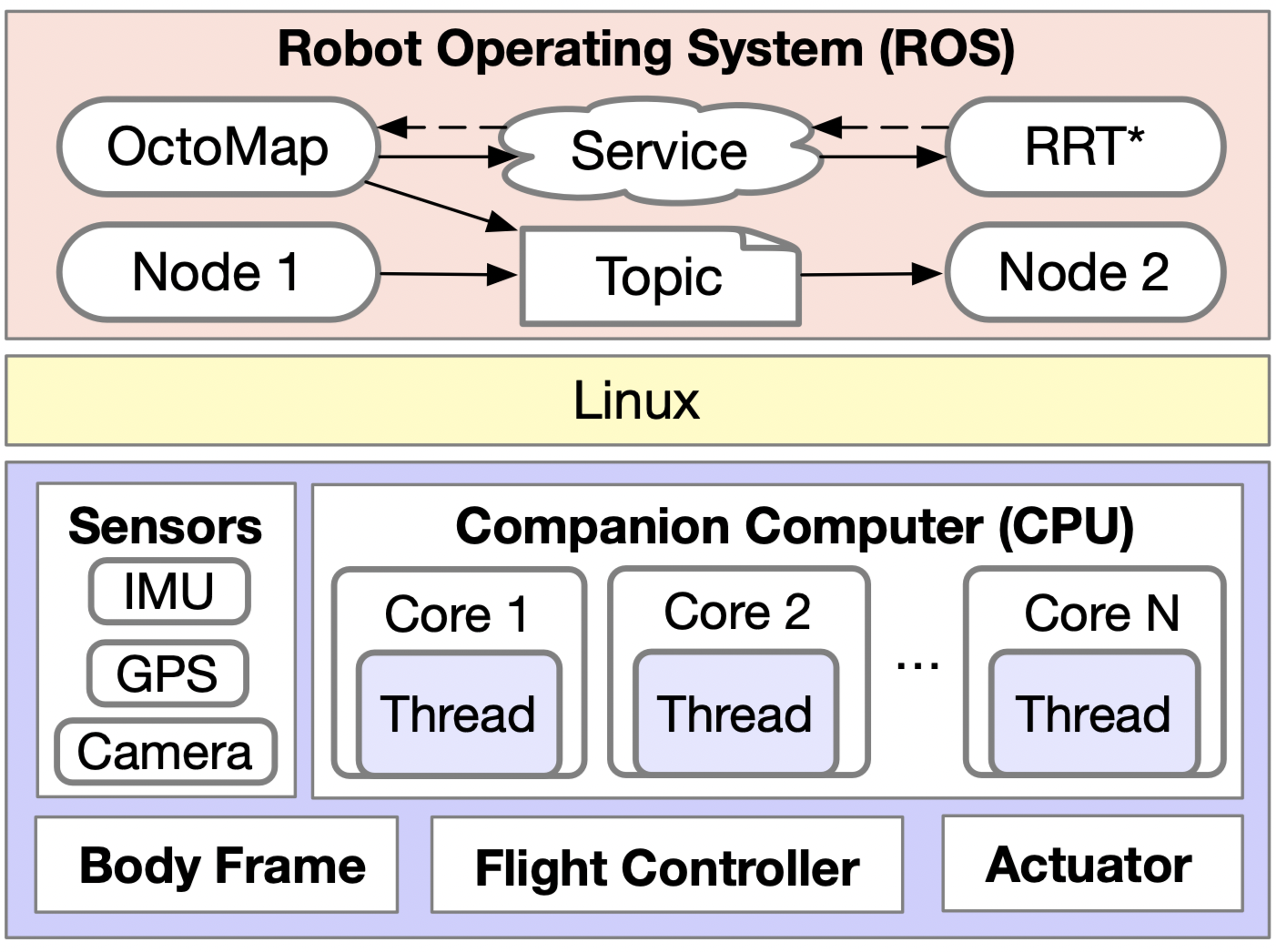

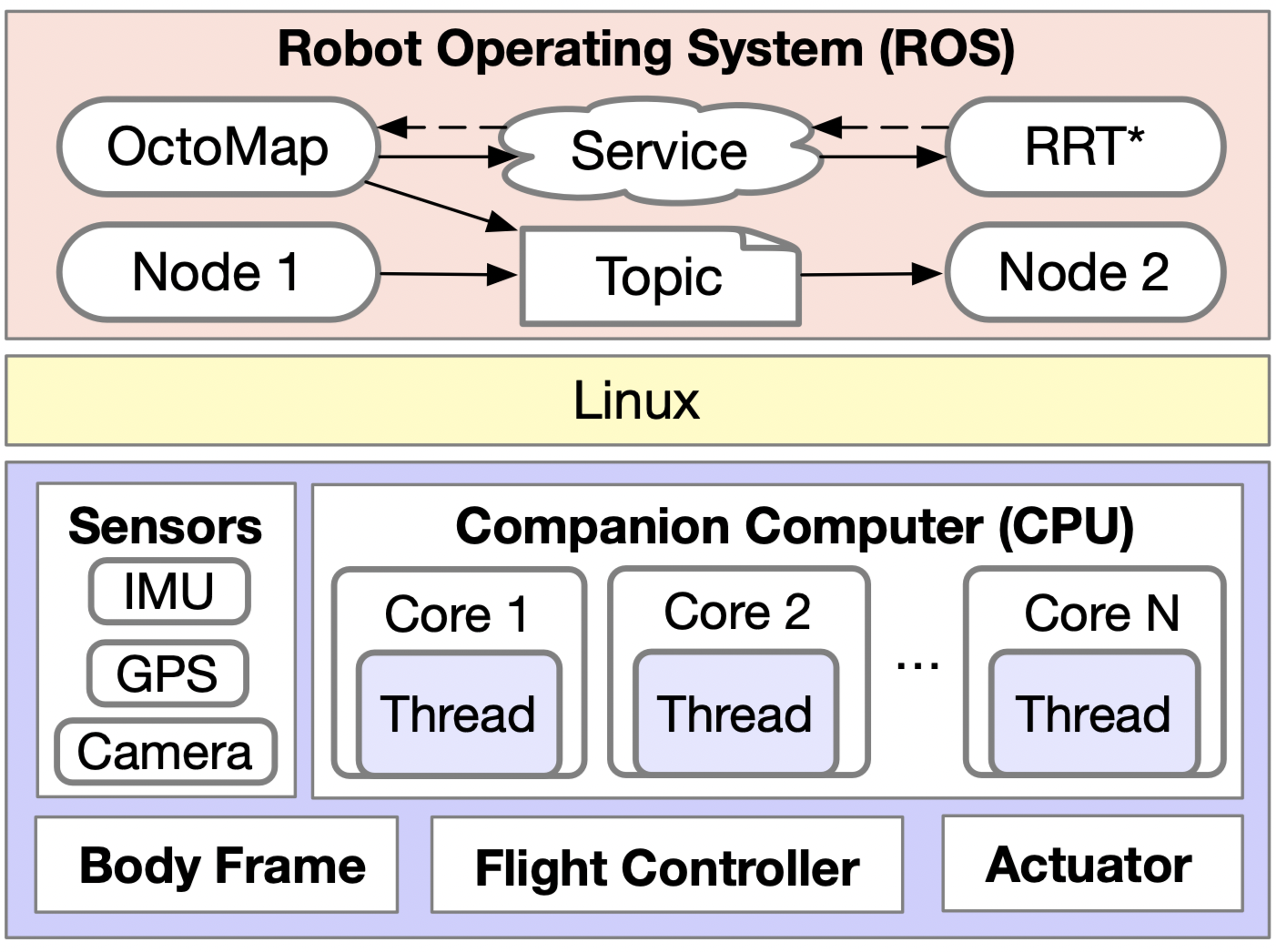

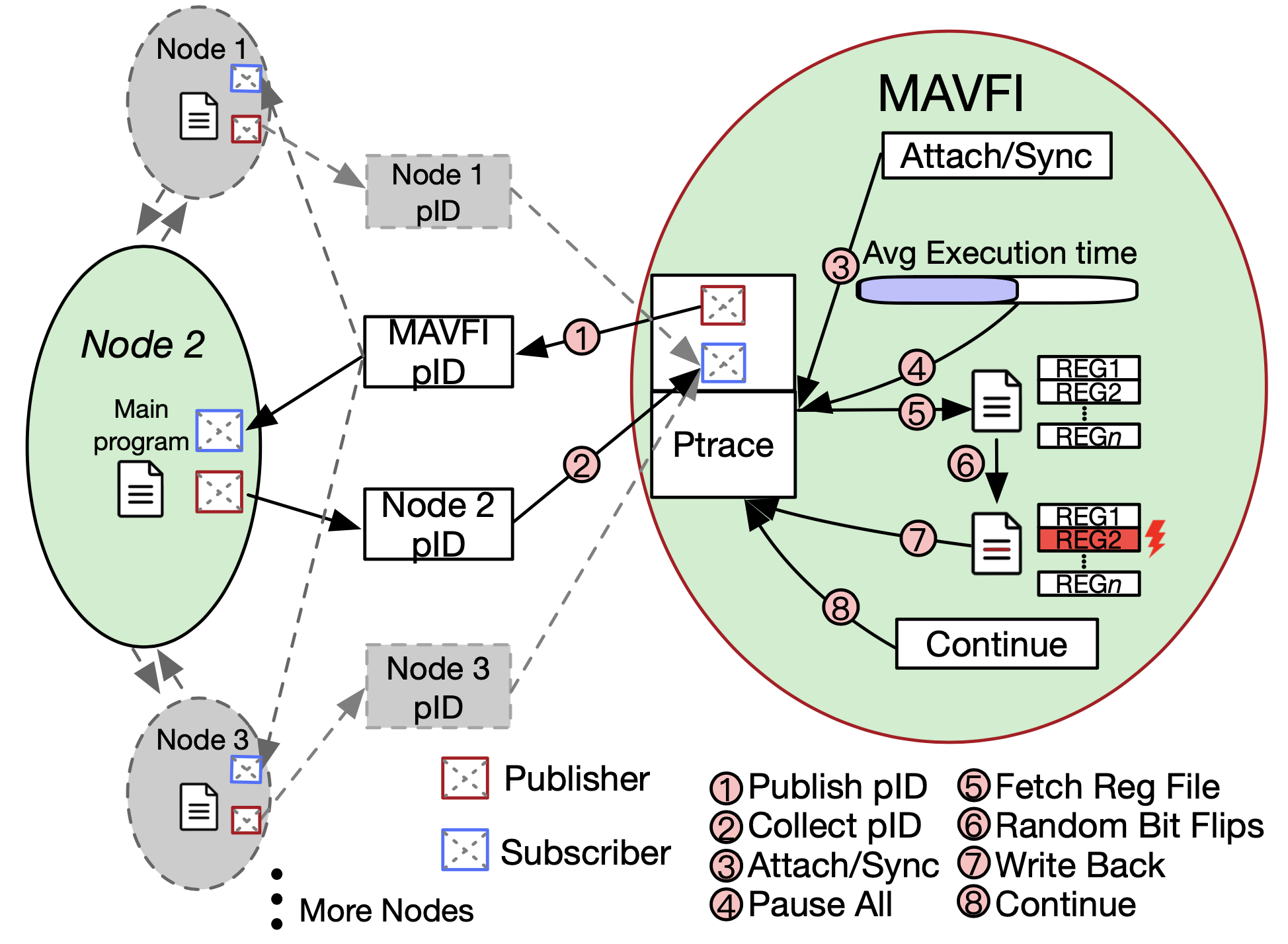

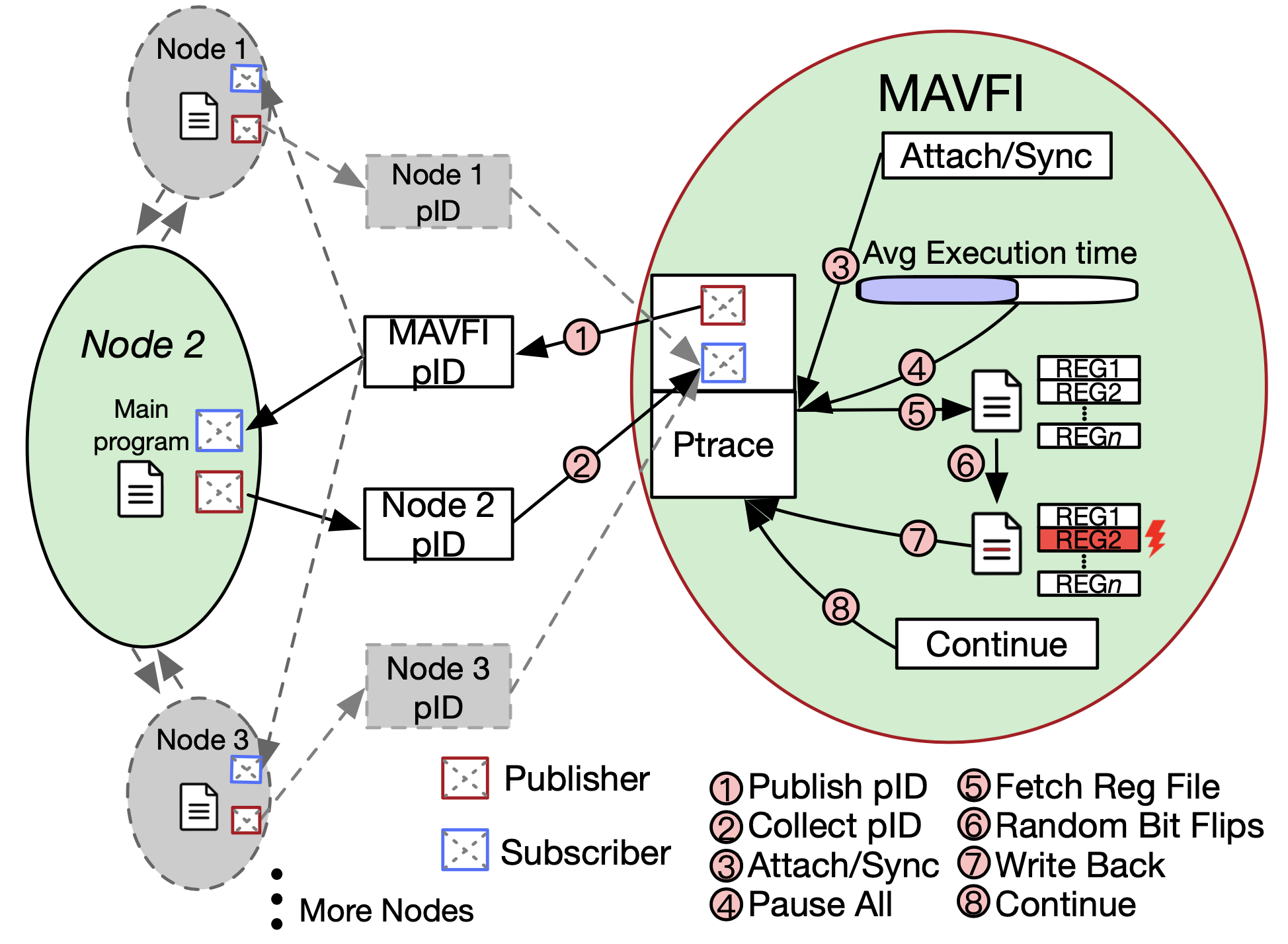

Yu-Shun Hsiao*, Zishen Wan*, Tianyu Jia, Radhika Ghosal, Abdulrahman Mahmoud, Arijit Raychowdhury, David Brooks, Gu-Yeon Wei, Vijay Janapa Reddi IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2023 Paper / Code We introduce ROSFI, the first Robot Operating System (ROS) resilience analysis methodology, to assess the effect of silent data corruption (SDC) on safety-critical applications. |

|

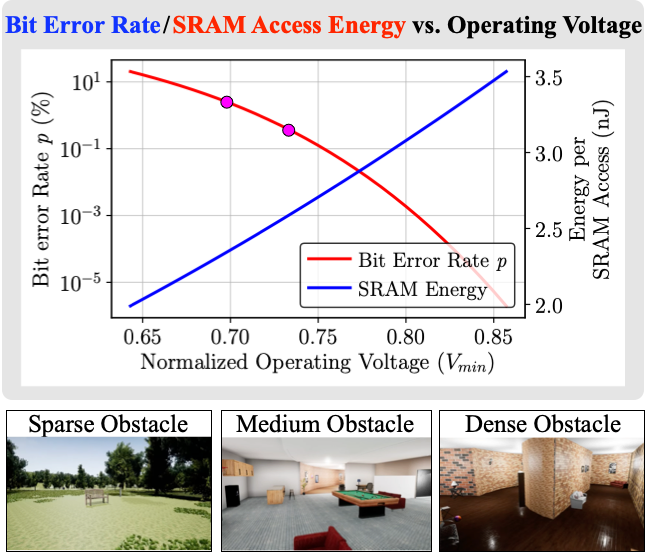

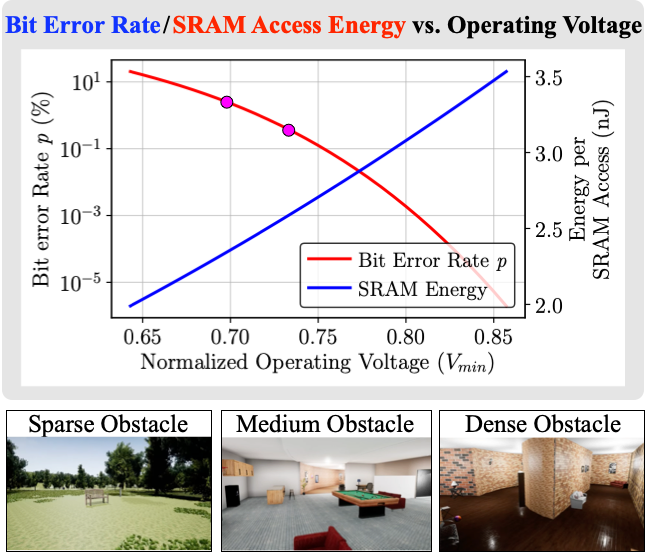

Zishen Wan, Nandhini Chandramoorthy, Karthik Swaminathan, Pin-Yu Chen, Vijay Janapa Reddi, Arijit Raychowdhury ACM/IEEE Design Automation Conference (DAC), 2023 Paper / Slide / Poster We propose BEERY, a robust learning framework to improve bit error robustness and energy efficiency for RL autonomous systems. BEERY enables robust low-voltage operation on UAVs, leading to high energy savings in both compute-level operation and system-level quality-of-flight. |

|

Yu-Shun Hsiao*, Zishen Wan*, Tianyu Jia, Radhika Ghosal, Abdulrahman Mahmoud, Arijit Raychowdhury, David Brooks, Gu-Yeon Wei, Vijay Janapa Reddi Design, Automation and Test in Europe Conference (DATE), 2023 Paper / Slide / Poster / Code We build a ROS-based end-to-end fault analysis framework to understand the resilience of Micro Aerial Vehicles (MAVs) system, and propose two low overhead anomaly-based transient fault detection and recovery schemes. |

|

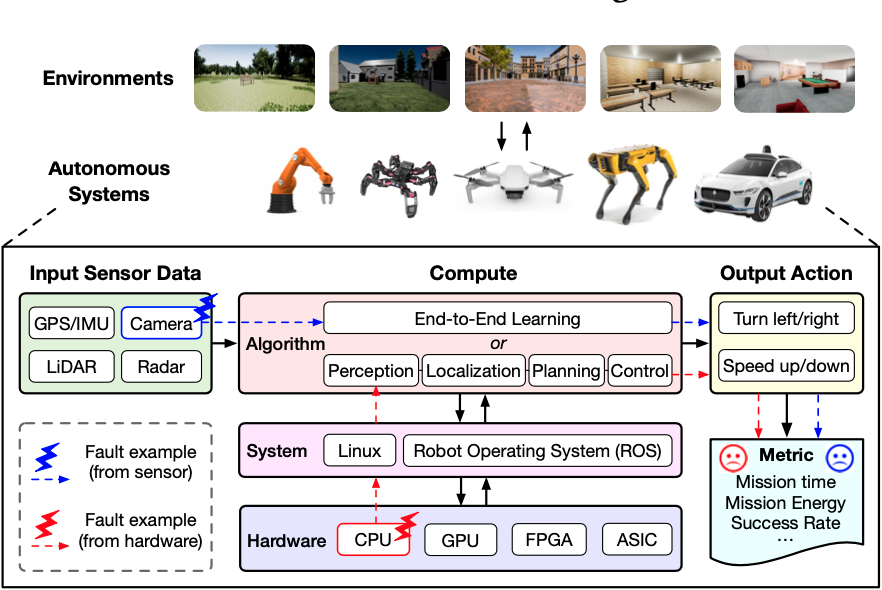

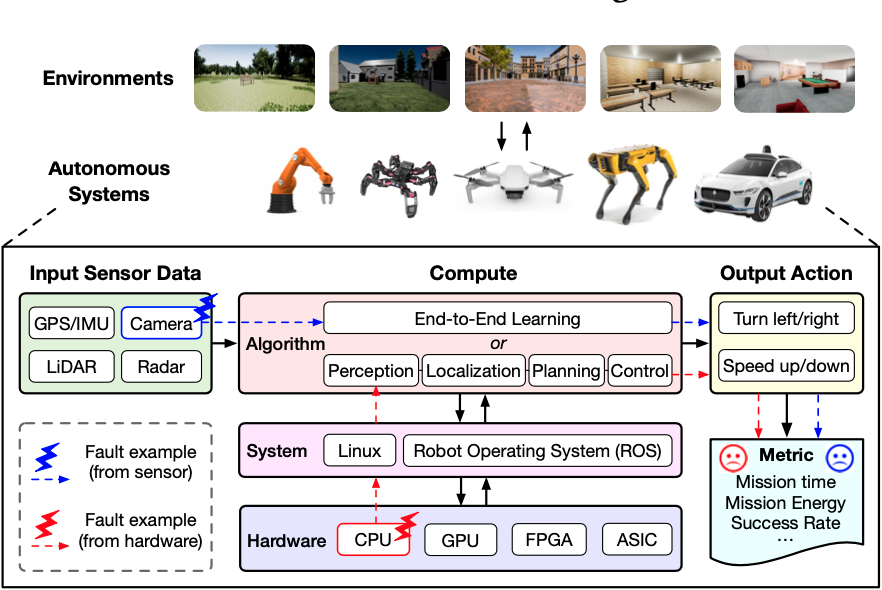

Zishen Wan, Karthik Swaminathan, Pin-Yu Chen, Nandhini Chandramoorthy, Arijit Raychowdhury IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2022 Paper / Media We explore the various originations of fault sources across the computing stack of autonomous systems, and discuss the diverse fault impacts and fault mitigation techniques of different scales of autonomous systems. |

|

Zishen Wan, Aqeel Anwar, Abdulrahman Mahmoud, Tianyu Jia, Yu-Shun Hsiao, Vijay Janapa Reddi, Arijit Raychowdhury Design, Automation and Test in Europe Conference (DATE), 2022 Paper / Slide We characterize the hardware transient fault impact on federated reinforcement learning system, a swarm intelligence paradigm in autonomous machines. We further propose application-aware cost-effective fault detection and mitigation scheme to enable autonomy reliability. |

|

Zishen Wan, Aqeel Anwar, Yu-Shun Hsiao, Tianyu Jia, Vijay Janapa Reddi, Arijit Raychowdhury ACM/IEEE Design Automation Conference (DAC), 2021 Best Presentation Award as DAC Young Fellow Paper / Slide / Video / Media We evaluate the resilience of learning-based navigation systems to transient and permanent hardware faults. We further propose two efficient fault mitigation techniques for both RL training and inference. |

|

Hardware Architecture of Autonomous Machine Computing |

|

Leshu Li, Jiayin Qin, Jie Peng, Zishen Wan, Huaizhi Qu, Ye Han, Pingqing Zheng, Hongsen Zhang, Yu (Kevin) Cao, Tianlong Chen, Yang (Katie) Zhao ACM/IEEE International Symposium on Microarchitecture (MICRO), 2025 Paper (To appear) We propose RTGS, an algorithm-hardware co-designed framework that enables real-time 3D Gaussian Splatting SLAM on edge devices by reducing multi-level computational redundancies. RTGS achieves real-time rendering performance through adaptive pruning, dynamic downsampling, and a GPU-integrated design. |

|

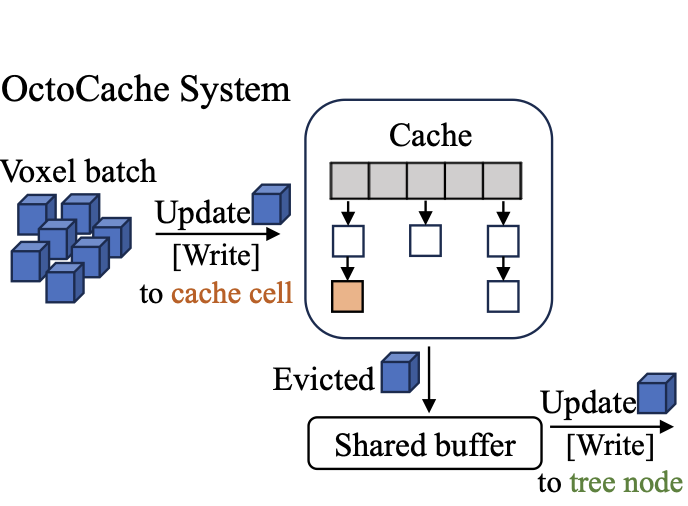

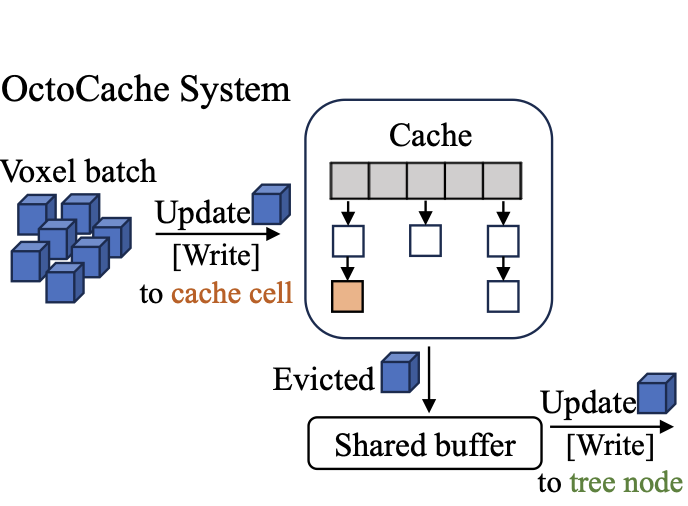

Peiqing Chen, Minghao Li, Zishen Wan, Yu-Shun Hsiao, Minlan Yu, Vijay Janapa Reddi, Zaoxing (Alan) Liu ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2025 Paper We propose OctoCache, a software system designed to accelerate 3D occupancy mapping performance in autonomous systems. OctoCache improves mapping system update speed through three mechanisms: (1) optimization of cache memory access, (2) refinement of voxel ordering, and (3) workflow parallelization. |

|

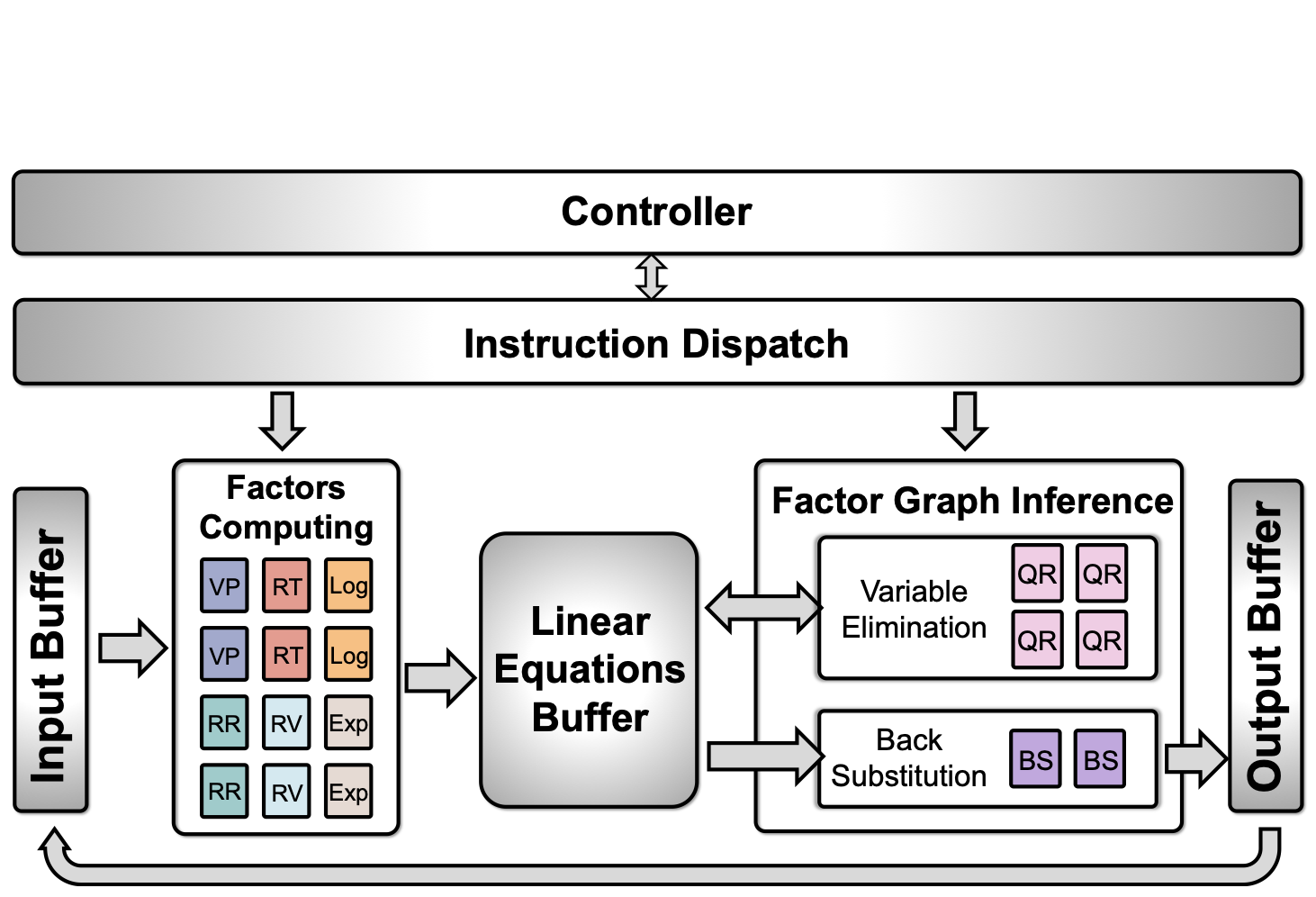

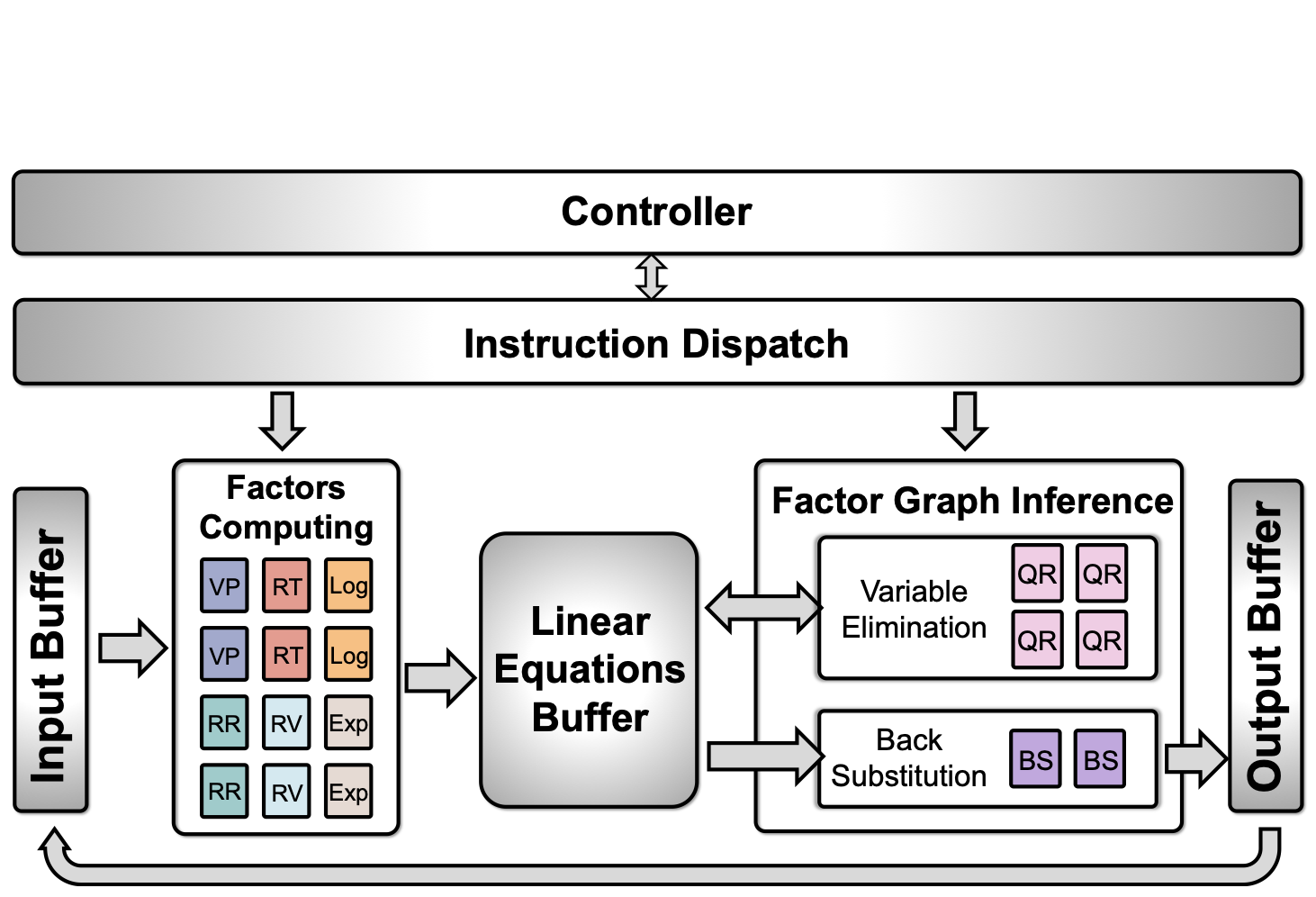

Yuhui Hao, Yiming Gan, Bo Yu, Qiang Liu, Yinhe Han, Zishen Wan, Shaoshan Liu ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2024 Paper / Lightning Talk / Poster We propose ORIANNA, a framework leverageing a common abstraction factor graph to generate accelerators for diverse robotic applications (e.g., manipulators, vehicles, drones) containing multiple optimization-based algorithms (e.g., localization, planning). |

|

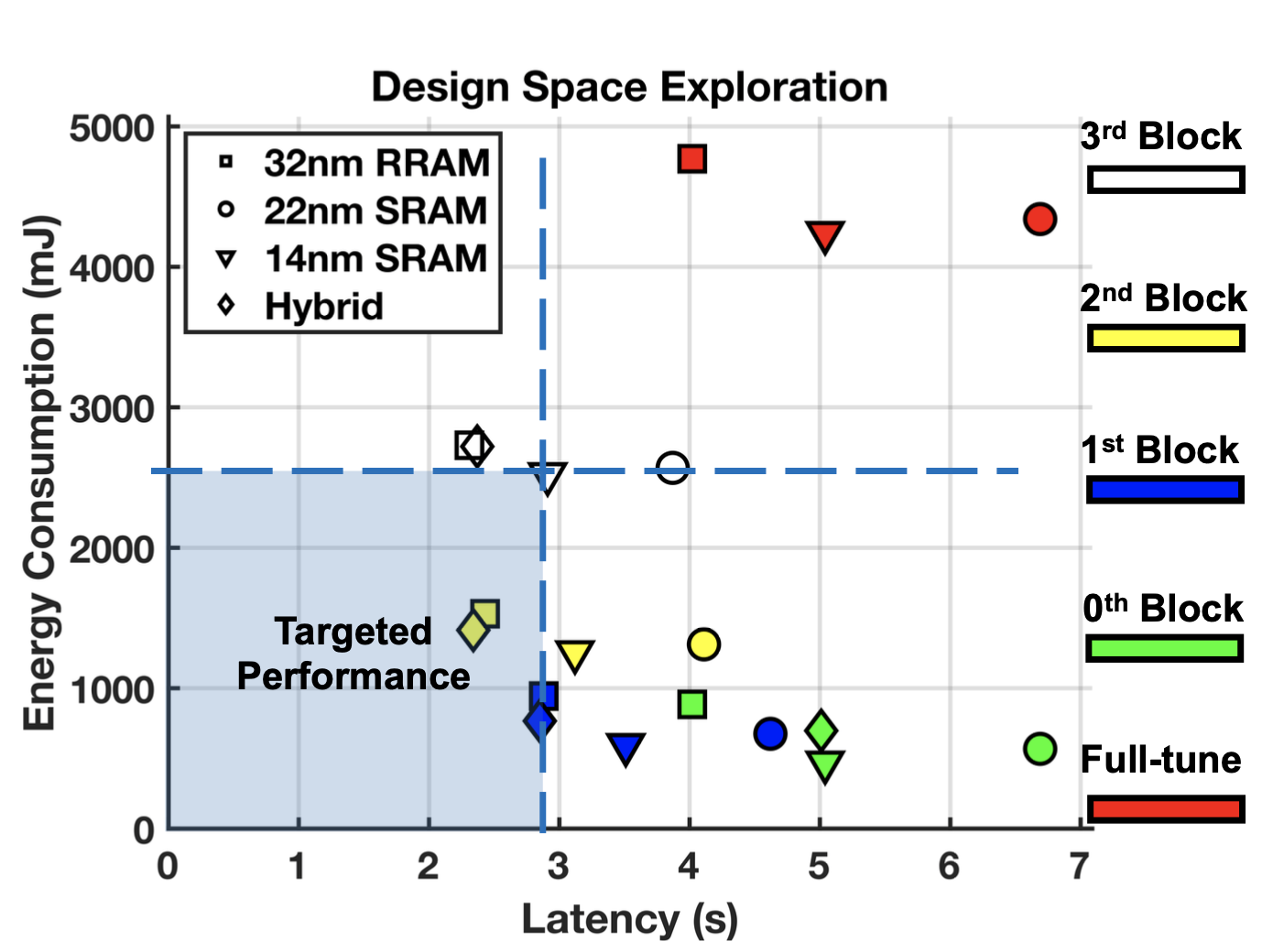

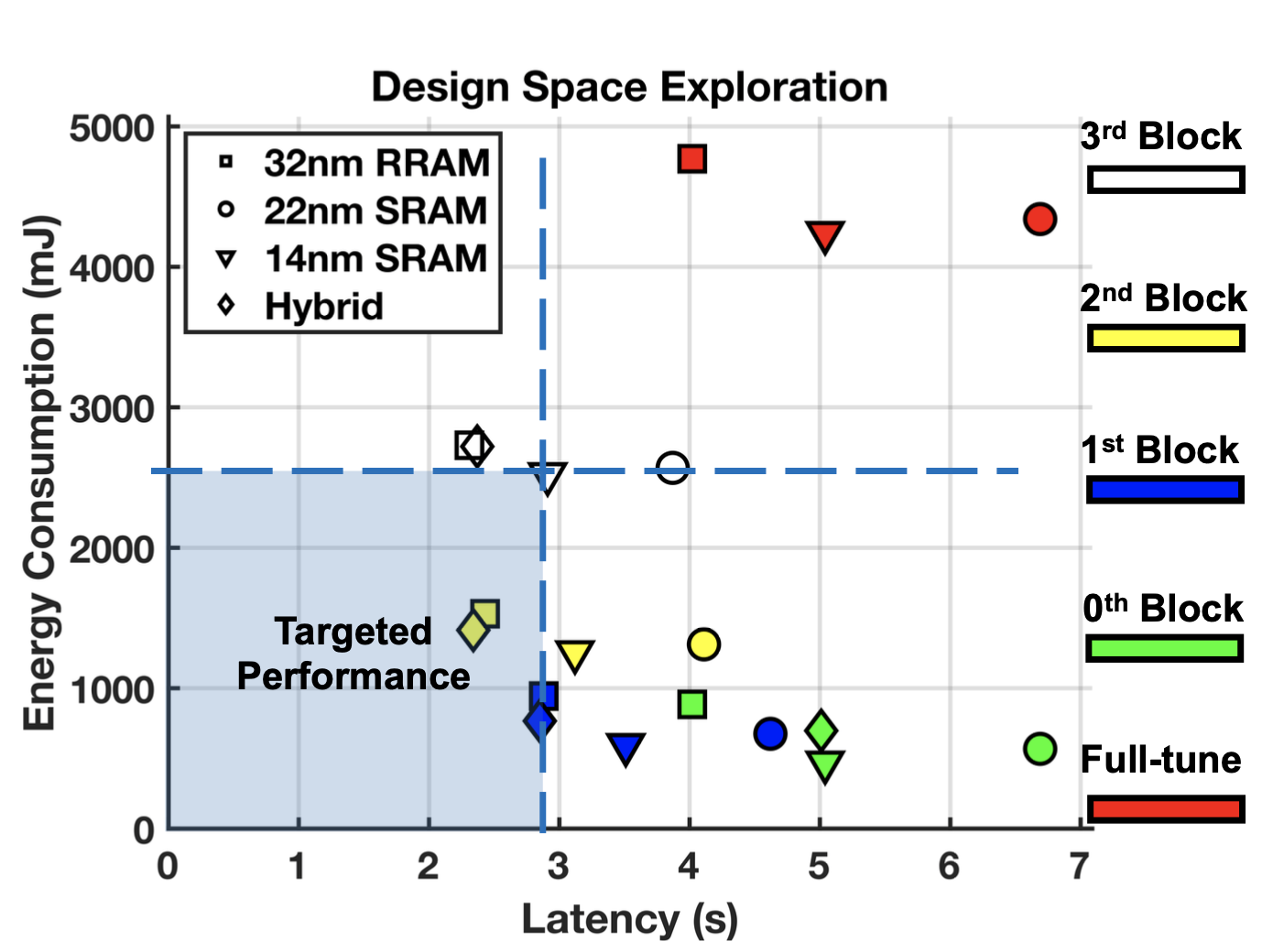

Zhenkun Fan*, Zishen Wan*, Che-Kai Liu, Anni Lu, Kshitij Bhardwaj, Arijit Raychowdhury ACM Journal on Autonomous Transportation Systems (JATS), 2024 Paper / Code We present a benchmarking framework and conduct a comprehensive measurement study of prediction-time DNN adaptation techniques, encompassing both supervised and unsupervised approaches, on CIM hardware substrates at the edge. |

|

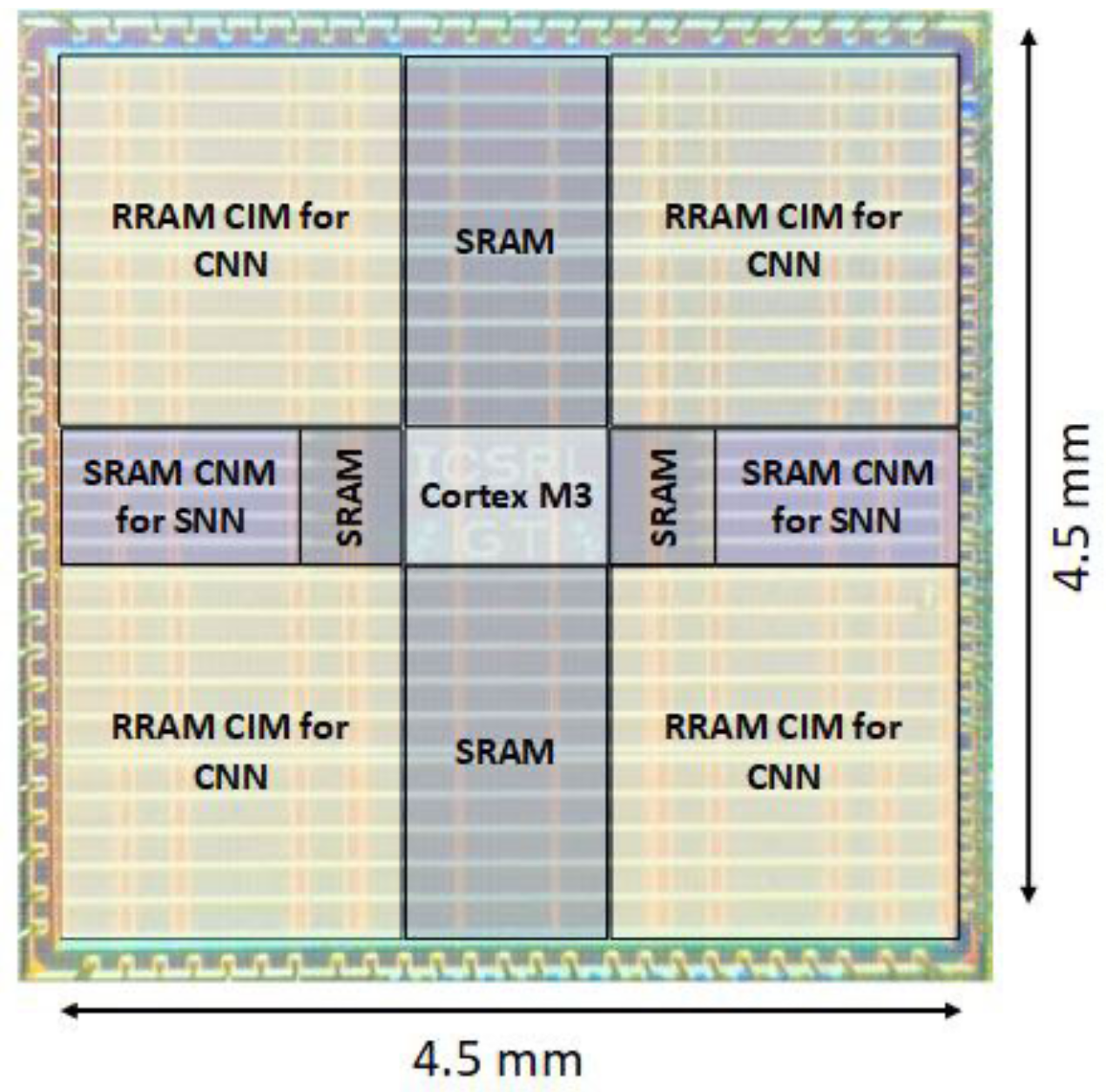

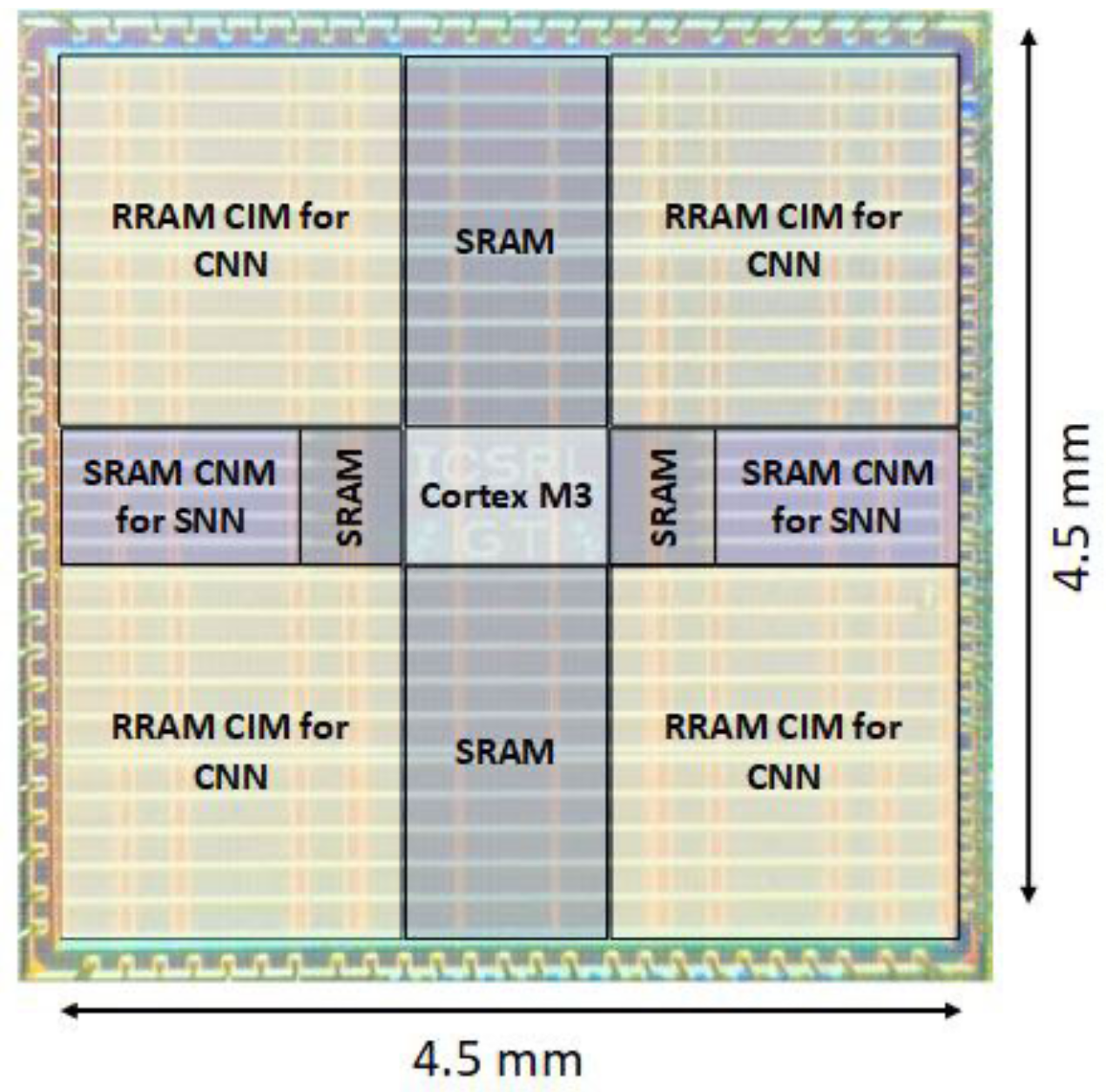

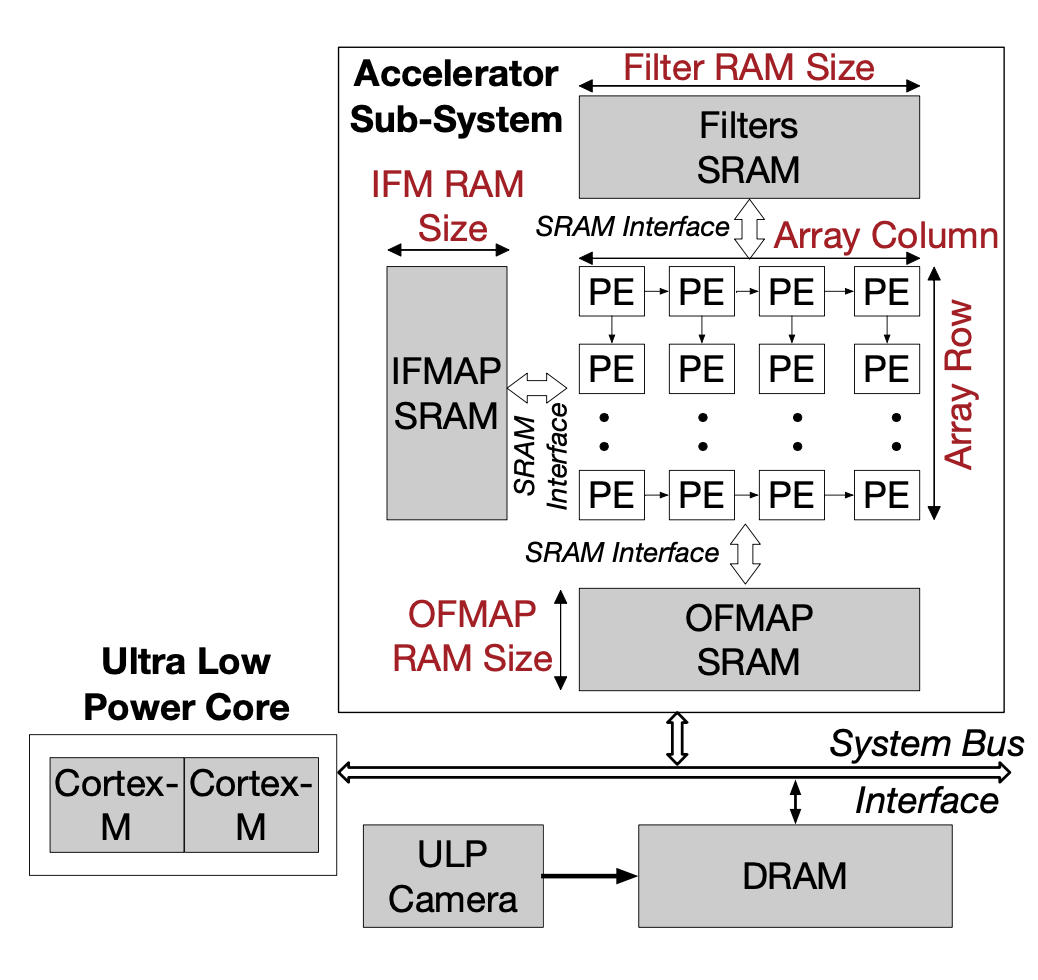

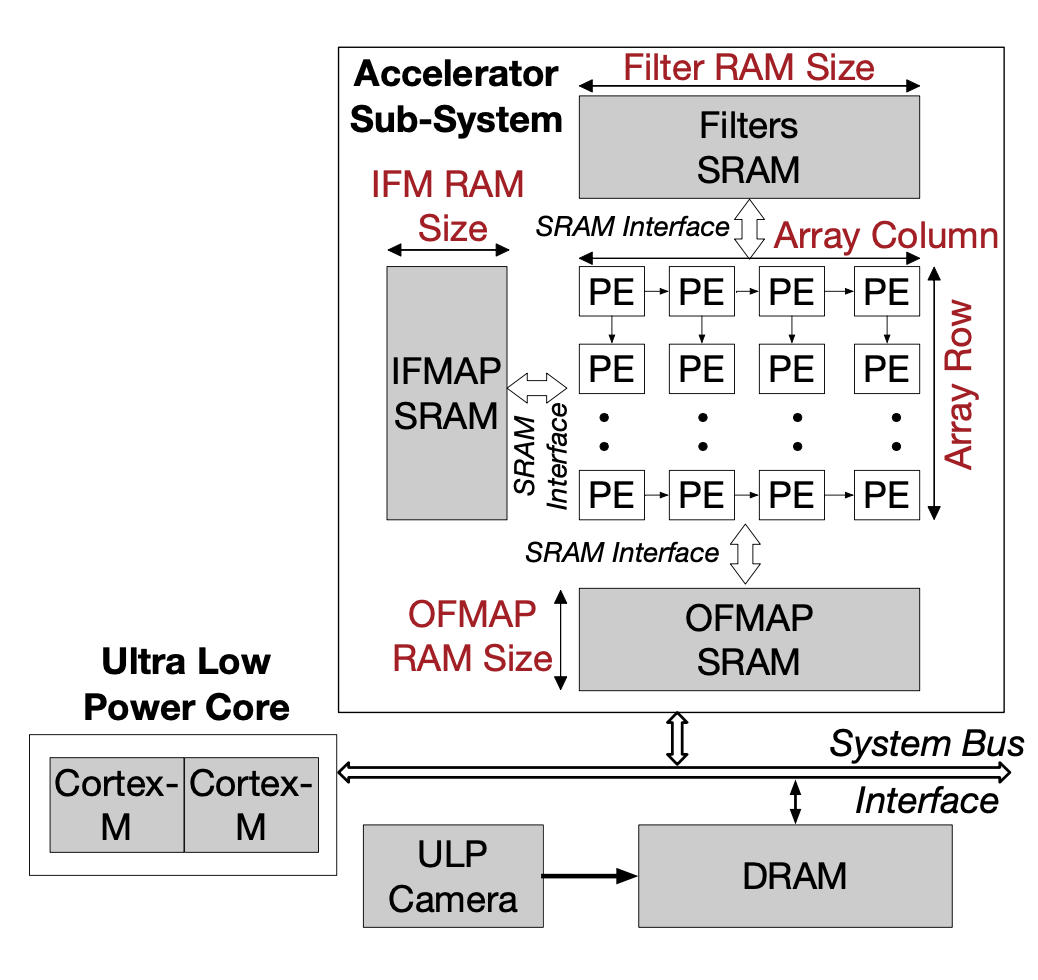

Ashwin Lele*, Muya Chang*, Samuel Spetalnick, Brian Crafton, Shota Konna, Zishen Wan, Ashwin Bhat, Win-San Khwa, Yu-der Chih, Meng-Fan Chang, Arijit Raychowdhury IEEE Journal of Solid-State Circuits (JSSC), 2023 Paper We present a heterogeneous programmable ARM Cortex-based SoC with power-efficient RRAM compute-in-memory for CNN and high-speed SRAM compute-near-memory for SNN for the modality-matched acceleration of the hybrid vision. |

|

Kshitij Bhardwaj, Zishen Wan, Arijit Raychowdhury, Ryan Goldhahn Design, Automation and Test in Europe Conference (DATE), 2023 Paper We propose a lightweight, fully unsupervised and real-time adaptation algorithm for safety-critical lane detection of autonomous driving, and demonstrate its state-of-the-art performance on Nvidia Jetson Orin. |

|

Muya Chang*, Ashwin Lele*, Samuel Spetalnick, Brian Crafton, Shota Konna, Zishen Wan, Ashwin Bhat, Win-San Khwa, Yu-der Chih, Meng-Fan Chang, Arijit Raychowdhury IEEE International Solid-State Circuits Conference (ISSCC), 2023 Paper We propose a fully-programmable heterogeneous ARM Cortex-based SoC with an in-memory low-power RRAM-based CNN and a near-memory high-speed SRAM-based SNN in a hybrid architecture, for high-speed target identification and tracking applications. |

|

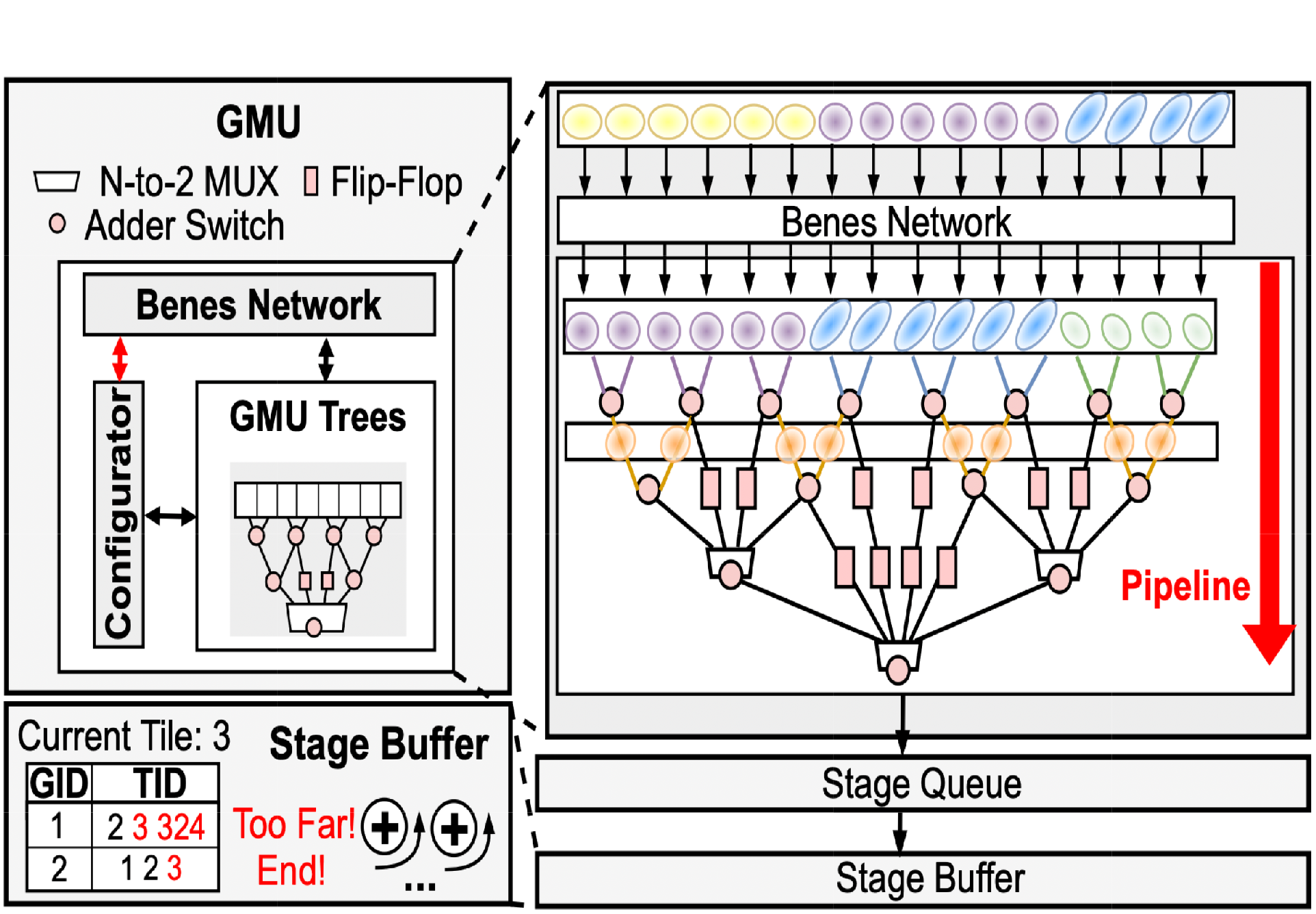

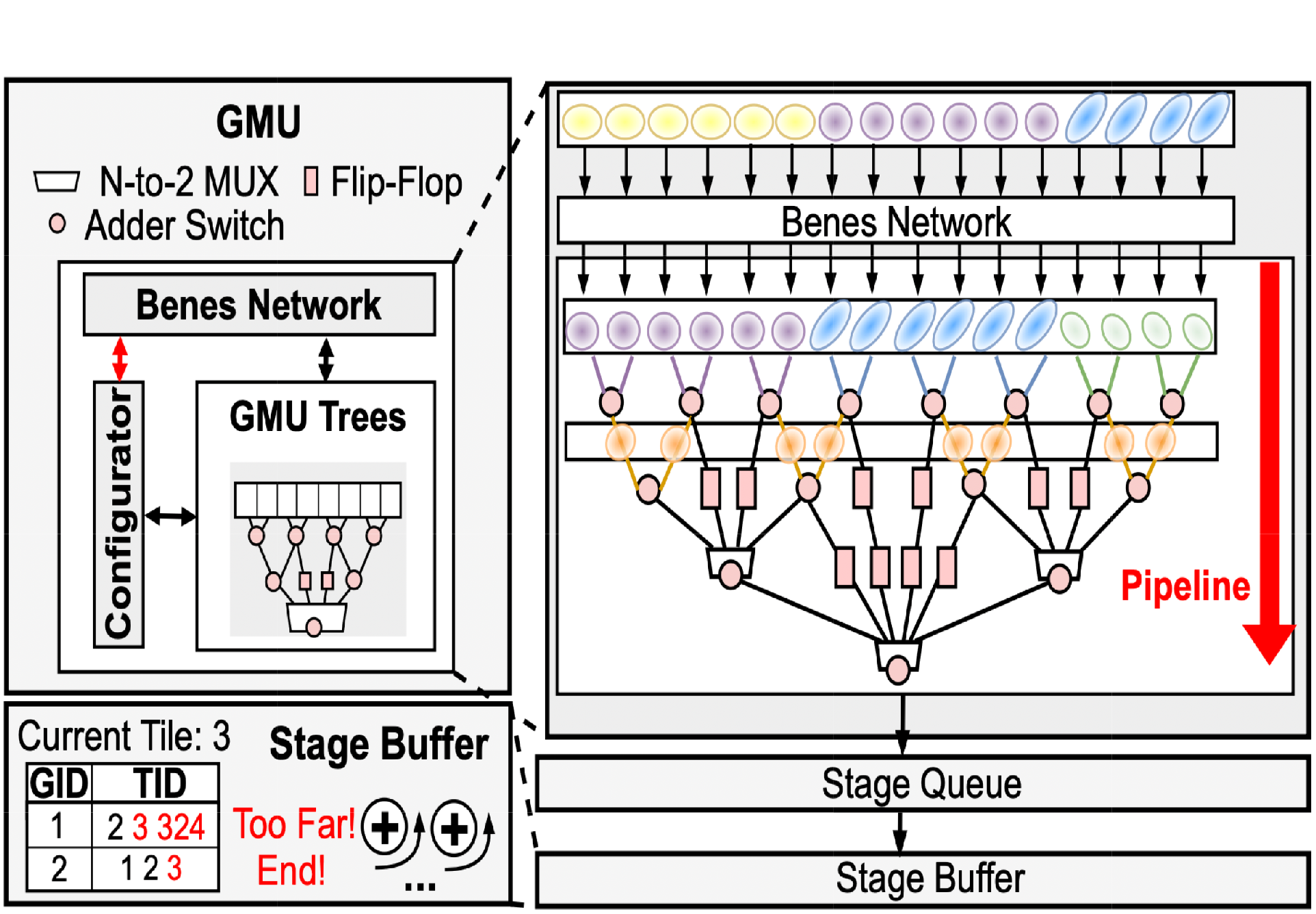

Qiang Liu*, Zishen Wan*, Bo Yu*, Weizhuang Liu, Shaoshan Liu, Arijit Raychowdhury IEEE Custom Integrated Circuits Conference (CICC), 2022 Paper / Slide We present an energy-efficient and runtime-reconfigurable FPGA-based accelerator for robotic localization tasks. We exploit SLAM-specific data locality, sparsity, reuse, and parallelism, and achieve >5x performance improvement over state-of-the-art. |

|

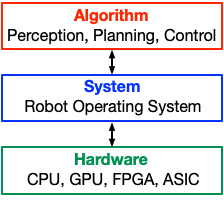

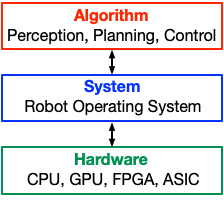

Zishen Wan, Ashwin Lele, Bo Yu, Shaoshan Liu, Yu Wang, Vijay Janapa Reddi, Cong (Callie) Hao, Arijit Raychowdhury IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2022 Paper / Slide / Video We present the cross-layer robotic computing stack, illustrate the current progress and key design techniques. We summarize and highlight the challenges, research opportunities, and roadmap for the next-generation FPGA-based robotic computing systems. |

|

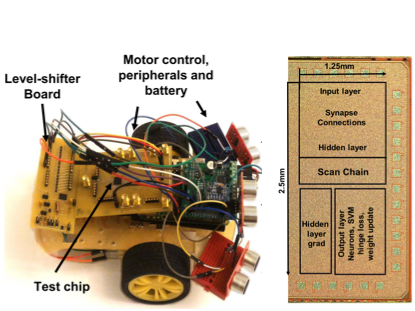

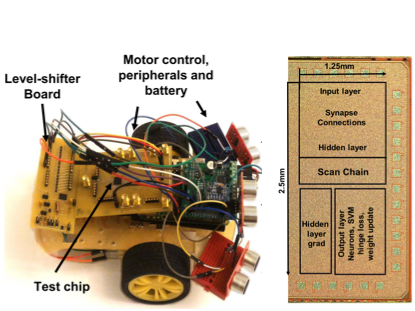

Zishen Wan, Ashwin Lele, Arijit Raychowdhury Asia and South Pacific Design Automation Conference (ASP-DAC), 2022 (Invited Paper) Paper / Slide We present a series of ultra-low-power accelerator and system designs on enabling the intelligence in edge robotic platforms, with an emphasis on mixed-signal circuit, neuro-inspired computing, benchmarking, software infrastructure, and algorithm-hardware co-design. |

|

Zishen Wan*, Bo Yu*, Thomas Yuang Li, Jie Tang, Yuhao Zhu, Yu Wang, Arijit Raychowdhury, Shaoshan Liu IEEE Circuits and Systems Magazine (CAS-M), 2021 Paper We provide an overview of recent work on FPGA-based robotic accelerators. An analysis of software and hardware optimization techniques and main technical issues is presented, along with some commercial and space applications. |

|

Zishen Wan*, Yuyang Zhang*, Arijit Raychowdhury, Bo Yu, Yanjun Zhang, Shaoshan Liu IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2021 Paper / Slide / Summary Video / Long Video We present a real-time and energy-efficient ORB (Oriented-Fast and Rotated-BRIEF) based visual system on FPGAs. Compared to Nvidia TX1 and Intel i7 CPU, our FPGA-based implementation achieves 5.6x and 3.4x speedup, as well as 3.0x and 34.6x power reduction, respectively. |

|

Tian Gao*, Zishen Wan*, Yuyang Zhang, Bo Yu, Yanjun Zhang, Shaoshan Liu, Arijit Raychowdhury IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2021 Paper We present an energy-efficient hardware architecture for real-time ELAS (Efficient Large-scale Stereo) based stereo matching on FPGAs. Compared to SOTA SoC and Intel i7 CPU, our FPGA design achieves 3.32x and 38.4x speedup, and 1.13x and 27.1x power reduction, respectively. |

|

Benchmarking and Design Flow of Autonomous Machine Computing |

|

Victor Mayoral-Vilches, Jason Jabbour, Yu-Shun Hsiao, Zishen Wan, Alejandra Martinez-Farina, Martino Crespo-Alvarez, Matthew Stewart, Juan Manuel Reina-Munoz, Prateek Nagras, Gaurav Vikhe, Mohammad Bakhshalipour, Martin Pinzger, Stefan Rass, Smruti Panigrahi, Giulio Corradi, Niladri Roy, Phillip B. Gibbons, Sabrina M. Neuman, Brian Plancher, Vijay Janapa Reddi IEEE International Conference on Robotics and Automation (ICRA), 2024 Best Paper Award, IROS Robotics Benchmarking Workshop 2023 Paper / Poster / Code / Project Page / Media We introduce RobotPerf, a benchmarking suite to evaluate robotics computing performance across a diverse range of hardware platforms. As an open-source initiative, RobotPerf remains committed to evolving with community input to advance the future of hardware-accelerated robotics. |

|

Zishen Wan, Vijay Janapa Reddi, Arijit Raychowdhury ACM Student Research Competition (SRC), Grand Final, 2023 First Place, ACM/SIGBED Student Research Competition (SRC) Paper / Slide / Media / Media This report summarizes our recent efforts in facilitating the development of scalable, efficient, adaptive, and reliable autonomous machine computing, including automatic domain-specific SoC exploration, software-hardware co-design, and performance-efficiency-resilience co-optimization. |

|

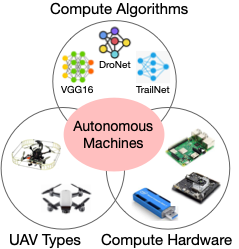

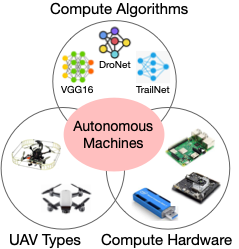

Srivatsan Krishnan, Zishen Wan, Kshitij Bhardwaj, Paul Whatmough, Aleksandra Faust, Sabrina M. Neuman, Gu-Yeon Wei, David Brooks, Vijay Janapa Reddi IEEE/ACM International Symposium on Microarchitecture (MICRO), 2022 IEEE Micro Top Picks 2023 Honorable Mention Paper / arXiv We propose a machine learning-based design space exploration framework, Autopilot, that can automate the full system cyber-physical co-design for aerial robots. AutoPilot consistently outperforms general-purpose processors and specialized accelerators built for drones. |

|

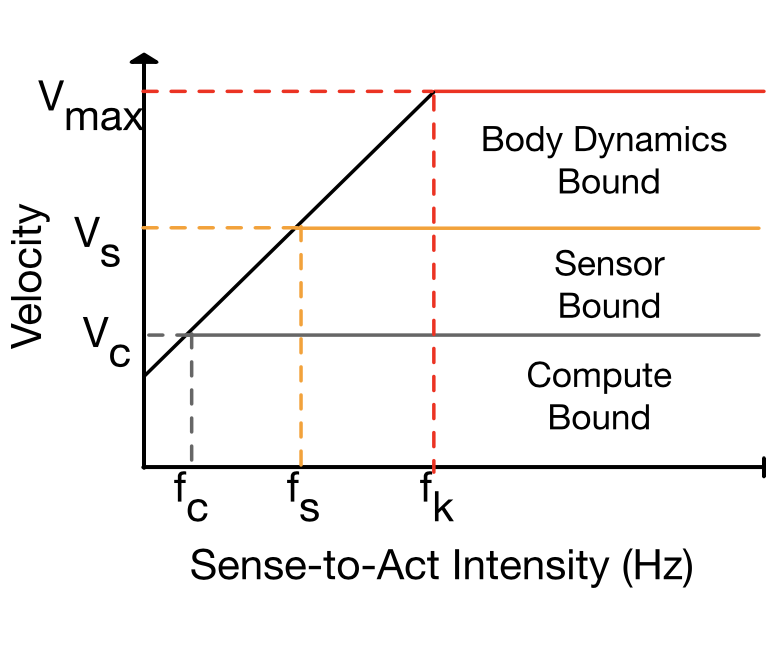

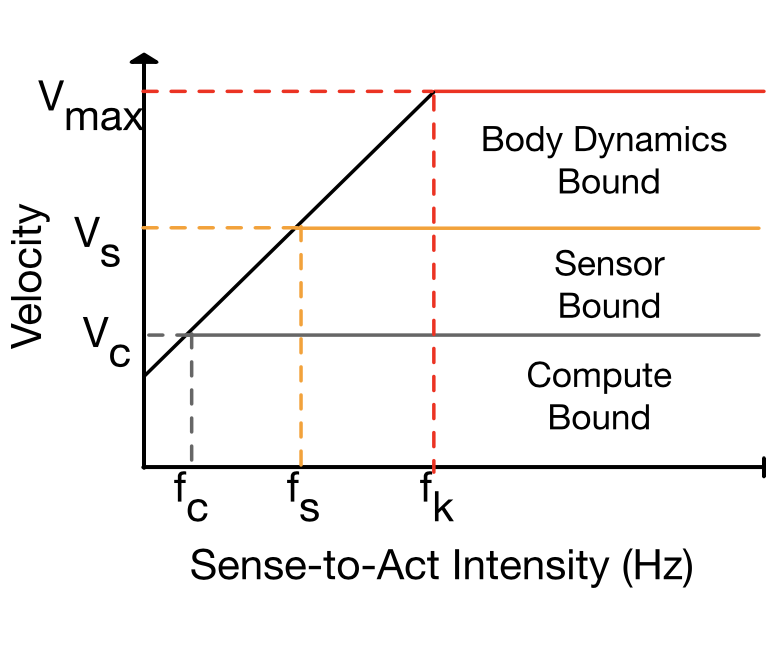

Srivatsan Krishnan, Zishen Wan, Kshitij Bhardwaj, Ninad Jadhav, Aleksandra Faust, Vijay Janapa Reddi IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2022 Paper / Skyline Tool We present a bottleneck analysis tool, Skyline, for designing compute systems for autonomous Unmanned Aerial Vehicles (UAV). The tool provides insights by exploiting the fundamental relationships between various components in the autonomous UAV such as sensor, compute, body dynamics. |

|

Srivatsan Krishnan, Thierry Tambe, Zishen Wan, Vijay Janapa Reddi Pre-print, 2021 Paper / Poster We present AutoSoC, a algorithms-hardware co-design framework for end-to-end learning-based aerial autonomous machines. AutoSoC runs the ASIC flow of place and route and generates layouts of the floor-planed accelerators with varying performance, area, and power consumption. |

|

Srivatsan Krishnan, Zishen Wan, Kshitij Bhardwaj, Paul Whatmough, Aleksandra Faust, Gu-Yeon Wei, David Brooks, Vijay Janapa Reddi IEEE Computer Architecture Letters (CAL), 2020 Best Paper Award Invited presentation at International Symposium on High-Performance Computer Architecture (HPCA), 2021 Paper / Tool Website We introduce a roofline-like model to understand the role of computing in aerial autonomous machines. The model provides insights by exploiting the fundamental relationships between various components in an aerial robot, such as sensor framerate, compute performance, and body dynamics. |