|

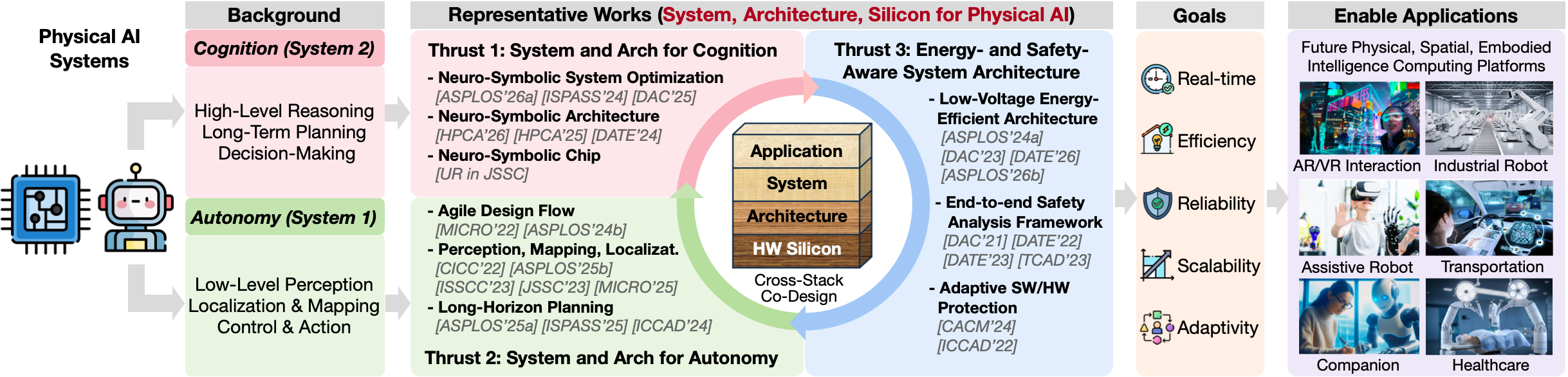

I am a Postdoc Fellow at Harvard University, working with Prof. Vijay Janapa Reddi. I received my Ph.D. from Georgia Tech (2025), advised by Prof. Arijit Raychowdhury and Prof. Tushar Krishna. I am a computer architect and SoC designer, working at the intersection of computer architecture, VLSI, and systems, with a focus on (1) cross-layer system-architecture-silicon co-design for embodied and physical AI, and (2) agentic AI for computing system design. My research has been supported by SRC JUMP centers CoCoSys and CBRIC, NSF, Qualcomm Fellowship, Baidu Fellowship, and CRNCH PhD Fellowship, and involves close collaboration with industry (e.g., IBM, TSMC, Intel, Google) and academia. My work has been recognized with Best Paper Awards at DAC, CAL, and SRC JUMP2.0, First Place in DAC PhD Forum, First Place in ACM Student Research Competition, and IEEE Micro Top Picks honorable mention. I was selected as 2023 ML and Systems Rising Star and 2024 Cyber-Physical Systems Rising Star. I am on the academic job market for the 2025-2026 cycle, and would appreciate any info about potential opportunities! Google Scholar / CV / LinkedIn / GitHub / ORCID |

Email: zishenwan@seas.harvard.edu zishenwan@gatech.edu |

|

|

|

|

|

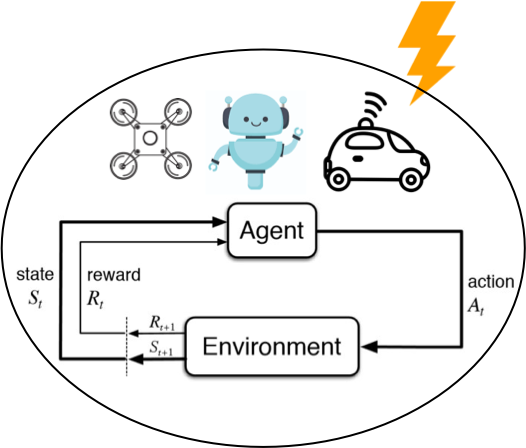

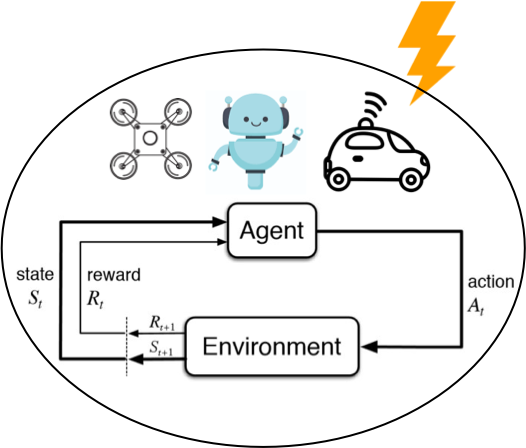

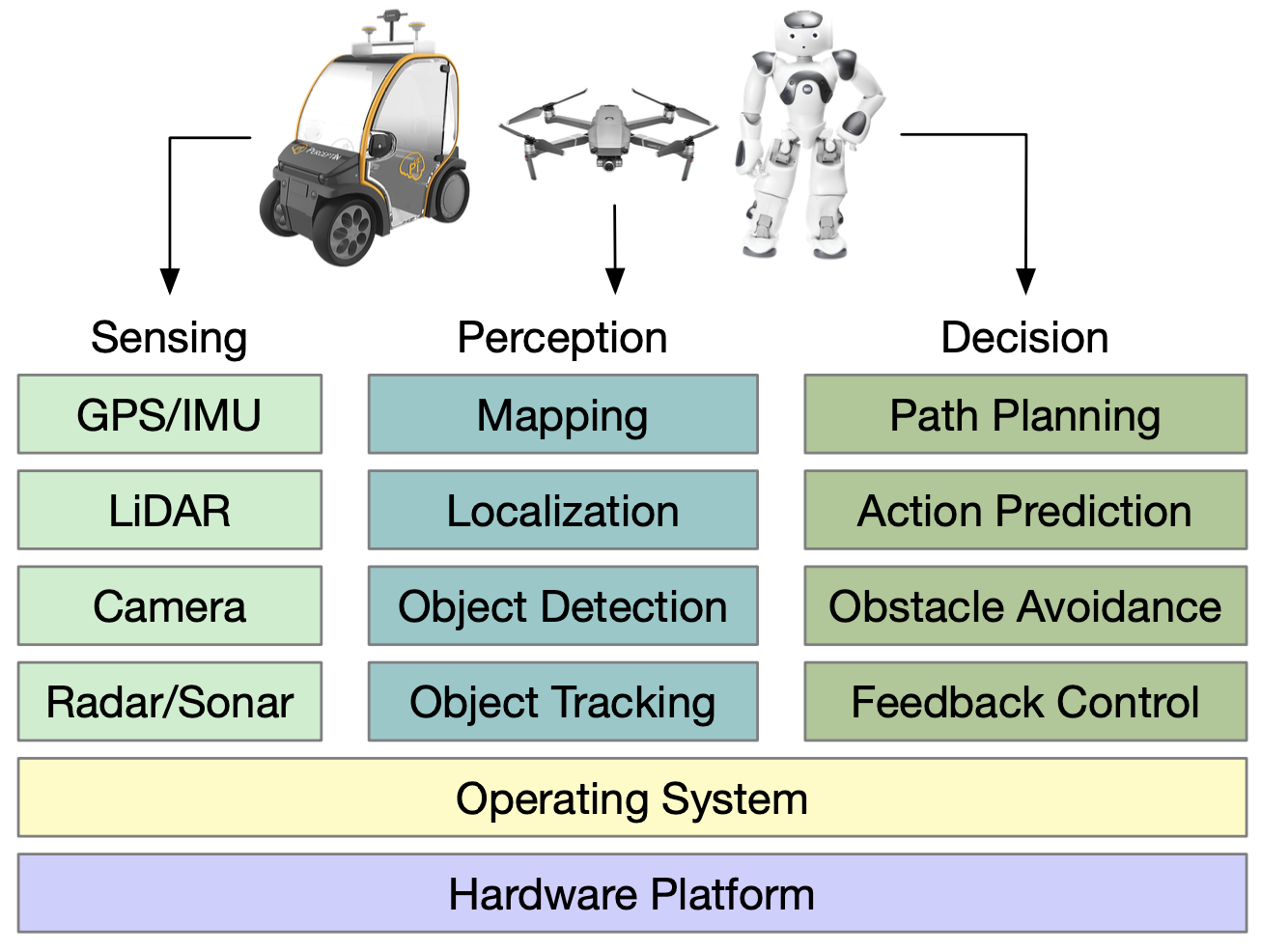

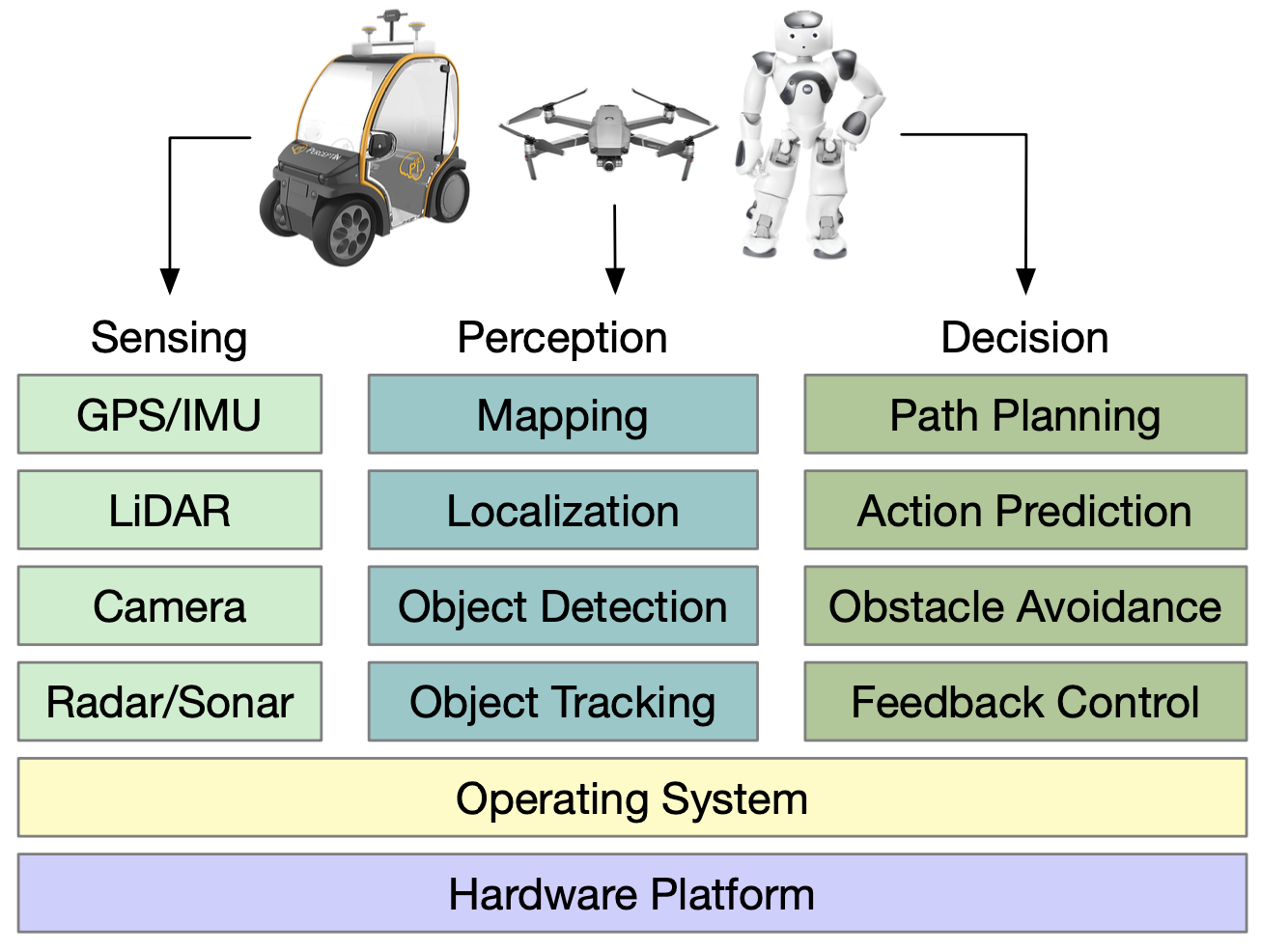

Shaoshan Liu, Zishen Wan, Bo Yu, Yu Wang Editor: Natalie Enright Jerger Synthesis Lectures on Computer Architecture (Morgan & Claypool Publishers), pp.1-218, Jun 2021 Book This book provides a thorough overview of the state-of-the-art FPGA-based robotic computing accelerator designs and summarizes their adopted optimized techniques. This book consists of ten chapters, delving into the details of how FPGAs have been utilized in robotic perception, localization, planning, and multi-robot collaboration tasks. In addition to individual robotic tasks, this book provides detailed descriptions of how FPGAs have been used in robotic products, including commercial autonomous vehicles and space exploration robots. Some key observations of this book has been published as a survey paper in IEEE Circuits and Systems Magazine, 2021. |

|

Vijay Janapa Reddi, Matthew Stewart, Ikechukwu Uchendu, Itai Shapira, Marcelo Rovai, Jayson Lin, Jeffrey Ma, Korneel Van den Berghe, Zishen Wan, Srivatsan Krishnan, Shvetank Prakash, Mark Mazumder, Colby Banbury, Jason Yik, Jessica Quaye, ... (contributor list) Book / GitHub This book is your gateway to the fast-paced world of AI systems through the lens of TinyML. This book aims to demystify the process of developing complete ML systems suitable for deployment - spanning key phases like data collection, model design, optimization, acceleration, security hardening, and integration. Crucial systems considerations like reliability, privacy, responsible AI, and solution validation are also explored in depth. This book is led by Prof. Vijay Janapa Reddi and resonates with Harvard TinyML course. Join us in this open-source collective effort - by the community, with the community, for the community. |

|

|

|

Zishen Wan, Vijay Janapa Reddi, Tushar Krishna, Arijit Raychowdhury Design Automation Conference (DAC) PhD Forum, 2025 First Place, ACM/IEEE DAC PhD Forum Poster / Media This poster presents tailored computing methodology for cross-layer software-system-hardware co-design to develop efficient, reliable, and adaptable architectures for embodied and neuro-symbolic intelligence. |

|

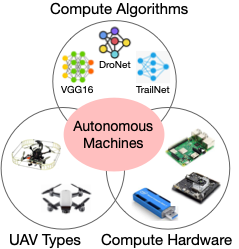

Zishen Wan, Vijay Janapa Reddi, Arijit Raychowdhury ACM Student Research Competition (SRC), Grand Final, 2023 First Place, ACM/SIGBED Student Research Competition (SRC) Paper / Slide / Media / Media This report summarizes our recent efforts in facilitating the development of scalable, efficient, adaptive, and reliable autonomous machine computing, including automatic domain-specific SoC exploration, software-hardware co-design, and performance-efficiency-resilience co-optimization. |

|

|

|

Arya Tschand*, Chenyu Wang*, Zishen Wan*, Andrew Cheng, Ioana Cristescu, Kevin He, Howard Huang, Alexander Ingare, Akseli Kangaslahti, Sara Kangaslahti, Theo Lebryk, Hongjin Lin, Jeffrey Jian Ma, Alexandru Meterez, Clara Mohri, Depen Morwani, Sunny Qin, Roy Rinberg, Paula Rodriguez-Diaz, Alyssa Mia Taliotis, Pernille Undrum Fathi, Rosie Zhao, Todd Zhou, Vijay Janapa Reddi arXiv preprint, 2026 Paper / Website This paper examines how generative AI can transform computing system design, identifying recurring cross-layer challenges and proposing principles for AI-driven co-design from software to silicon. |

|

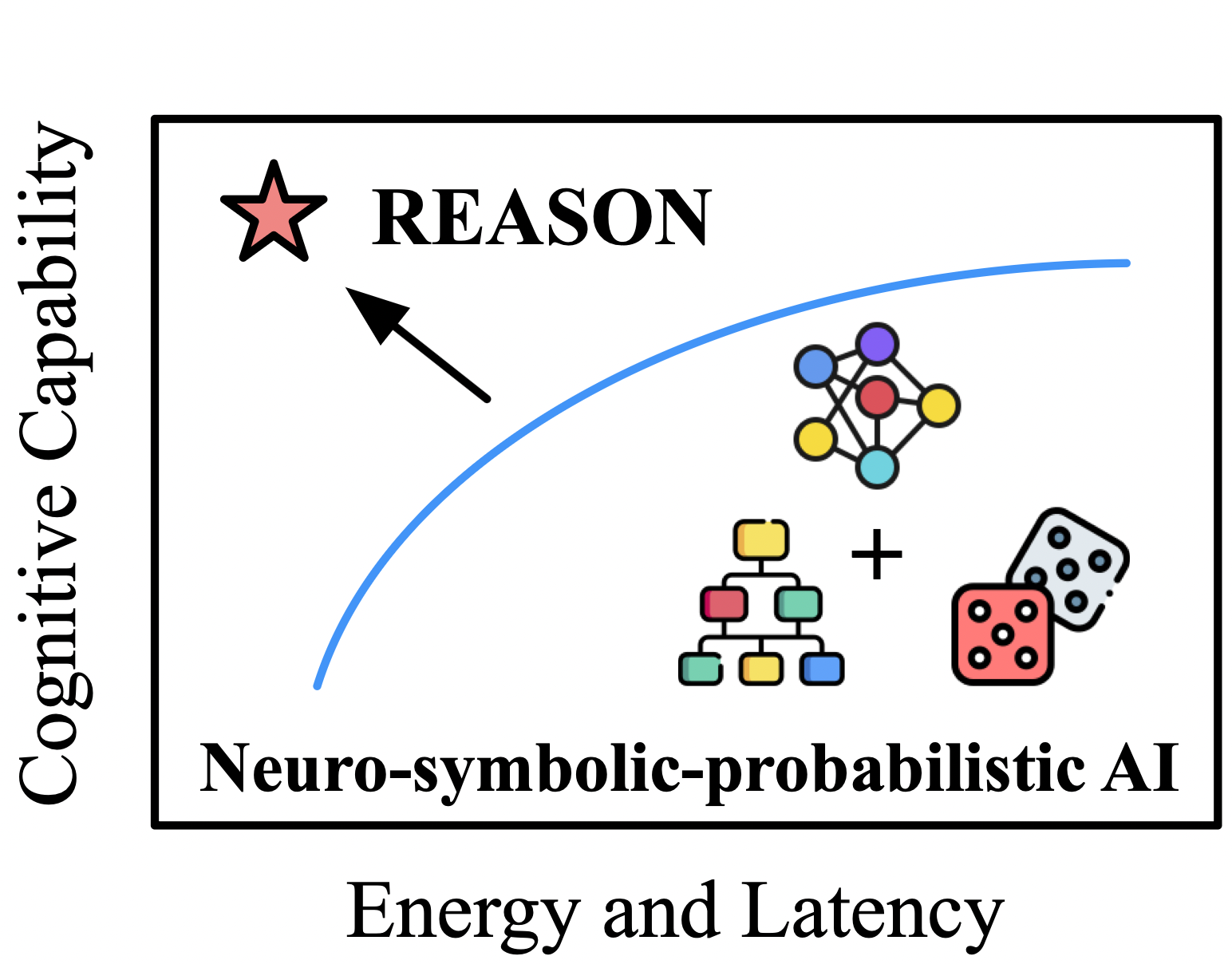

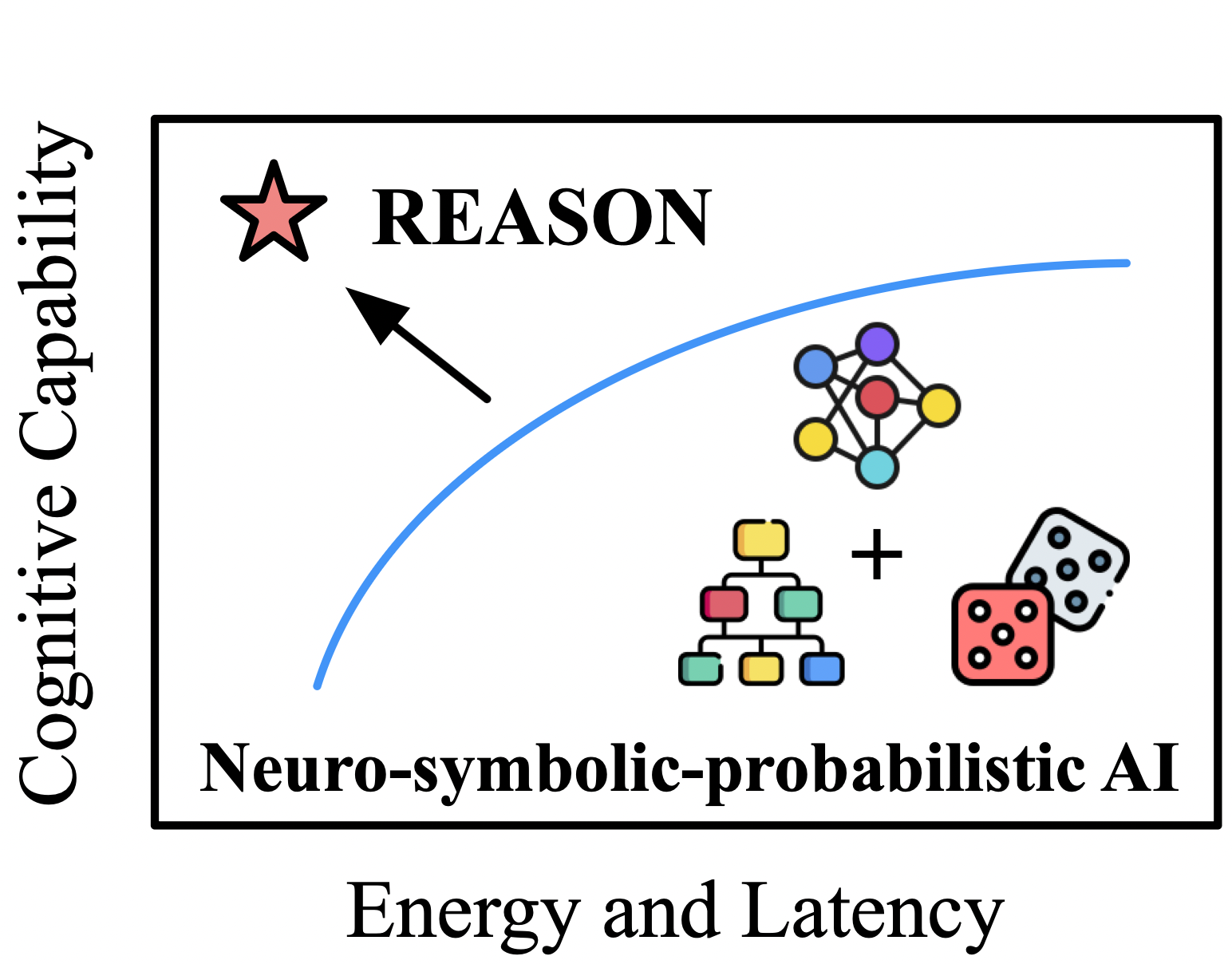

Zishen Wan, Che-Kai Liu, Jiayi Qian, Hanchen Yang, Arijit Raychowdhury, Tushar Krishna International Symposium on High-Performance Computer Architecture (HPCA), 2026 Paper / Slide / Talk / Tutorial / Media REASON is an algorithm-system-architecture framework that accelerates the “slow-thinking” components of cognitive AI -- logical deduction, constraint solving, and probabilistic reasoning -- through common representation, reconfigurable architecture, and tight GPU integration for LLM+symbolic agentic workflows. |

|

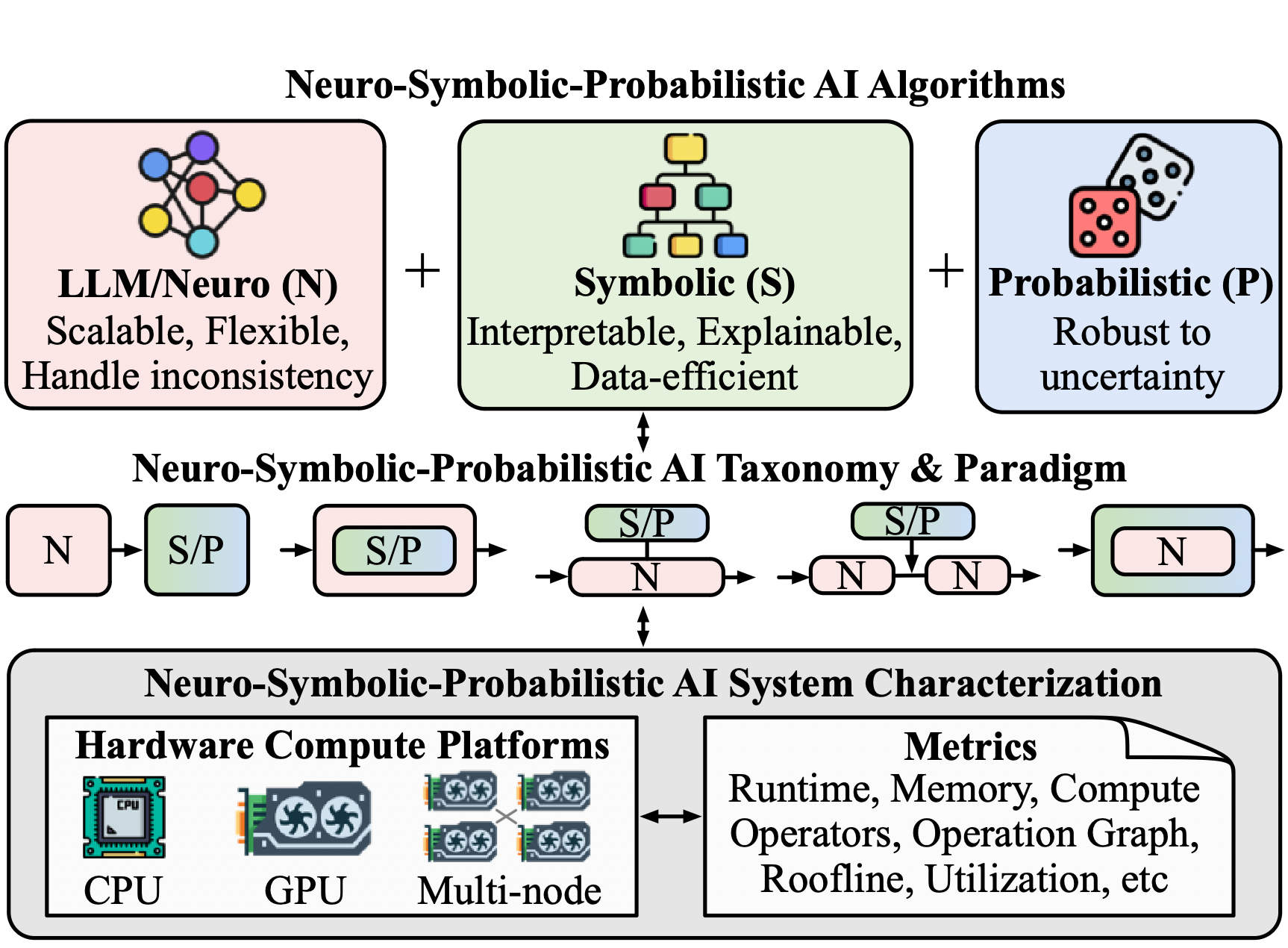

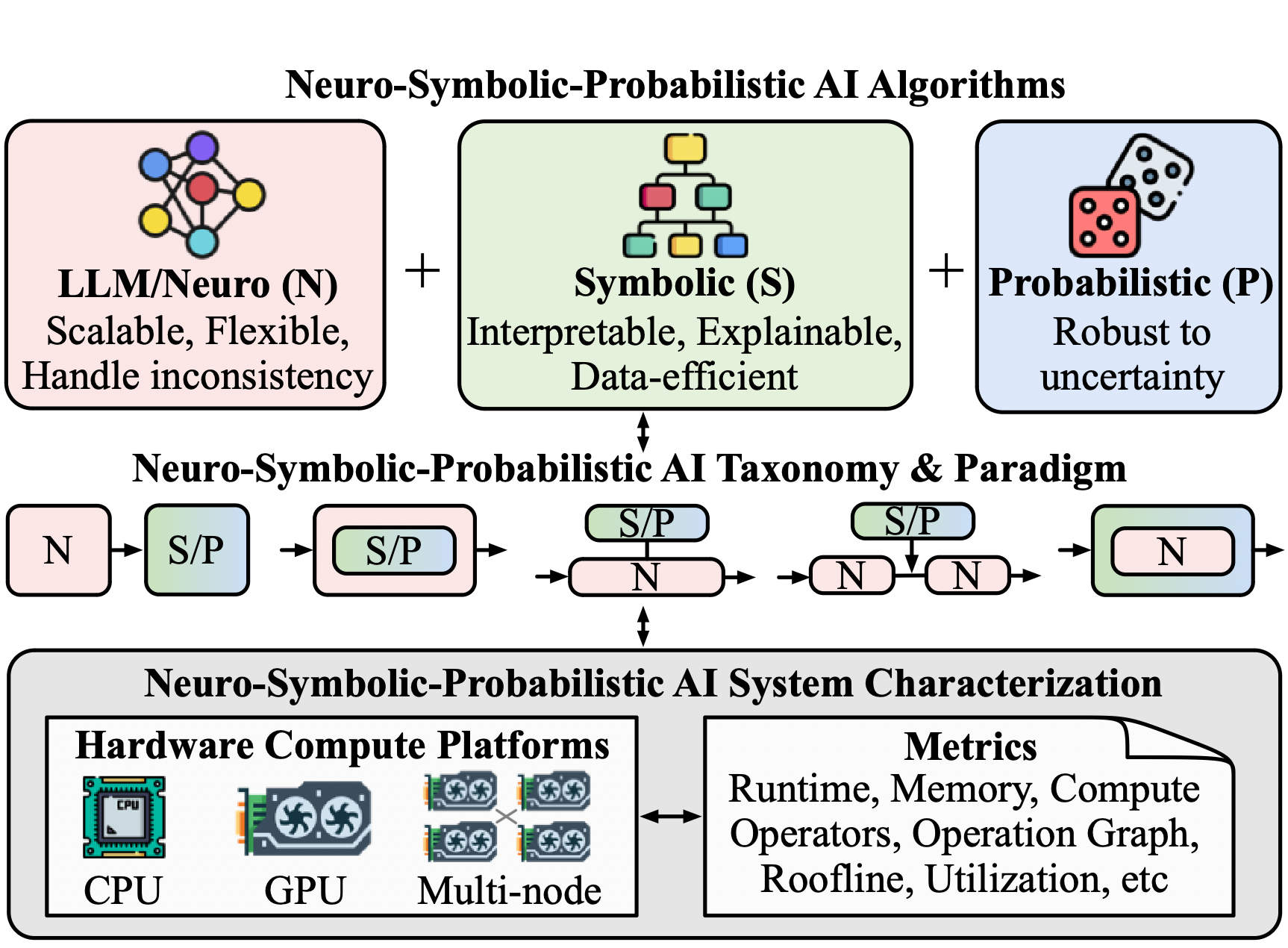

Zishen Wan, Hanchen Yang, Jiayi Qian, Ritik Raj, Joongun Park, Chenyu Wang, Arijit Raychowdhury, Tushar Krishna ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2026 Best Paper Award, DARPA SRC JUMP 2.0, 2025 Paper Compositional AI integrates LLMs, symbolic, and probabilistic modules to enhance interpretability, robustness, and trustworthiness for cognitive applications. This paper presents a comprehensive system-level analysis of neuro-symbolic-probabilistic AI and reveals its key performance characteristics. |

|

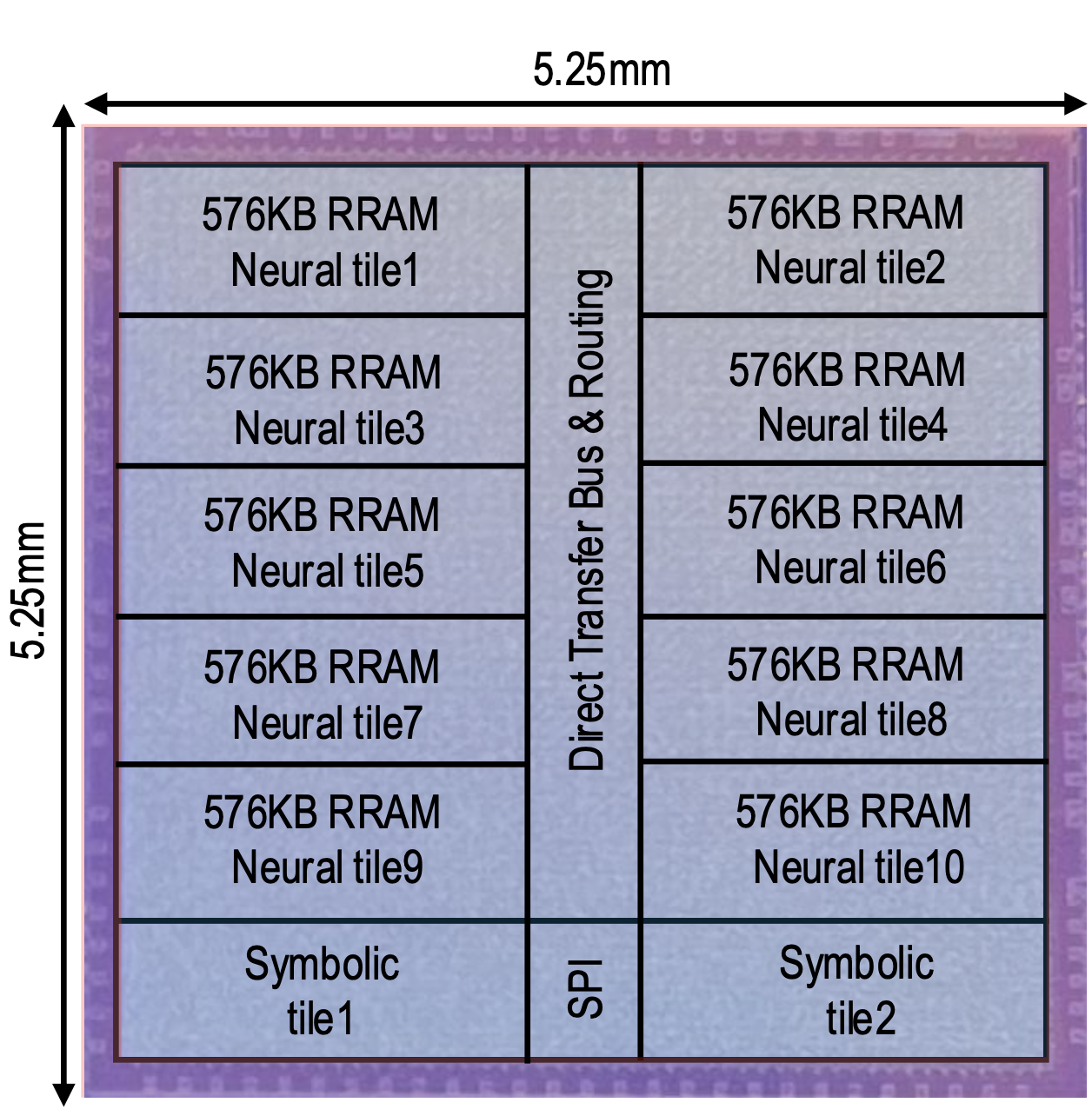

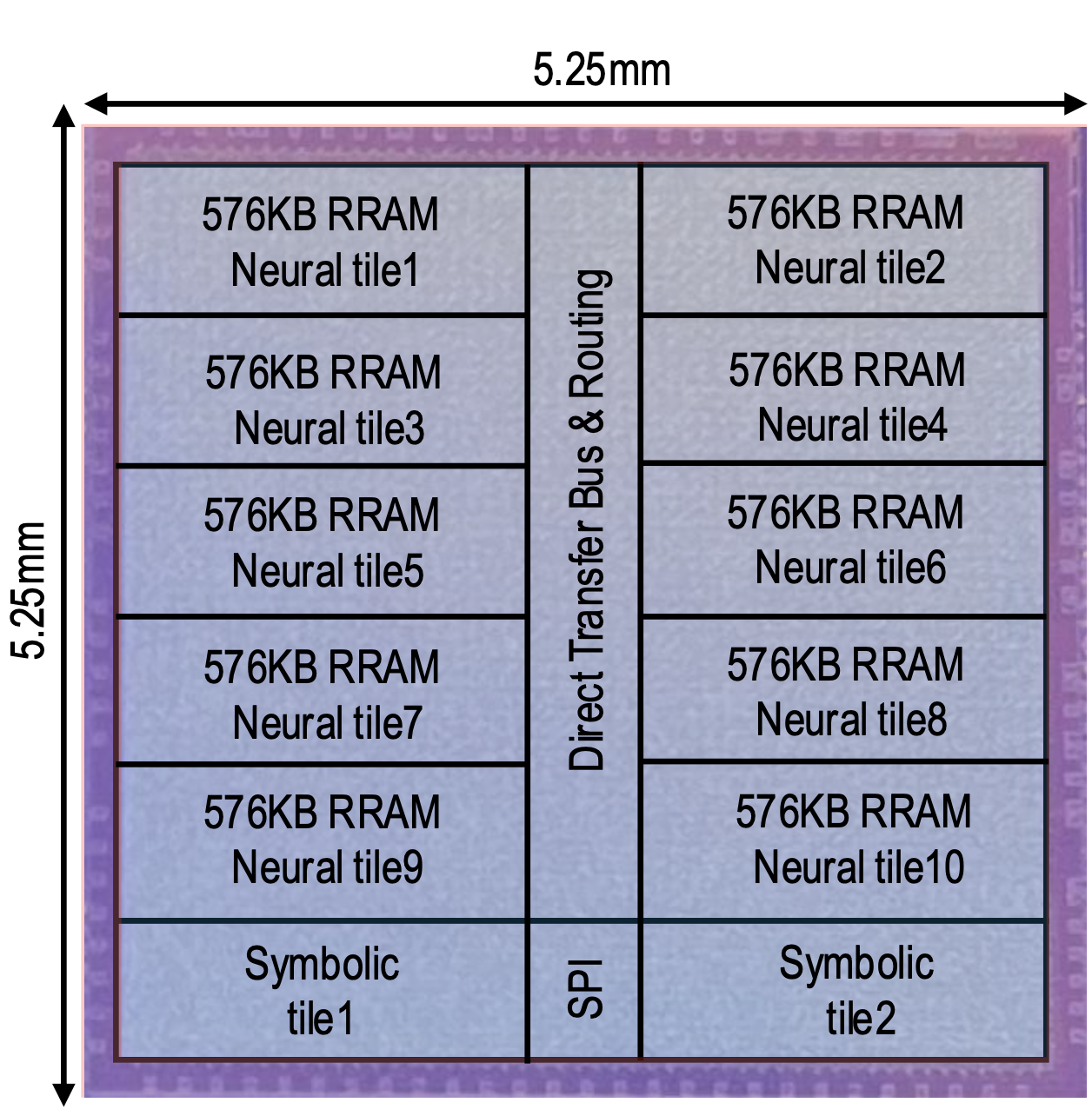

Che-Kai Liu*, Zishen Wan*, Young-Seok Noh, Mohamed Ibrahim, Samuel D. Spetalnick, Tushar Krishna, Win-San Khwa, Ashwin Sanjay Lele, Yu-Der Chih, Meng-Fan Chang, Arijit Raychowdhury IEEE Journal of Solid-State Circuits (JSSC), 2026 Paper (To appear) We tape out a fully programmable heterogeneous SoC that integrates RRAM/SRAM to efficiently accelerate a broad class of neuro-symbolic workloads. The chip features integrated RRAM and SRAM neural-symbolic data paths, ultra-dense RRAM macros, scheduler-informed power management, and flexible programming support, demonstrating end-to-end silicon system for generalizable and efficient neuro-symbolic AI inference. |

|

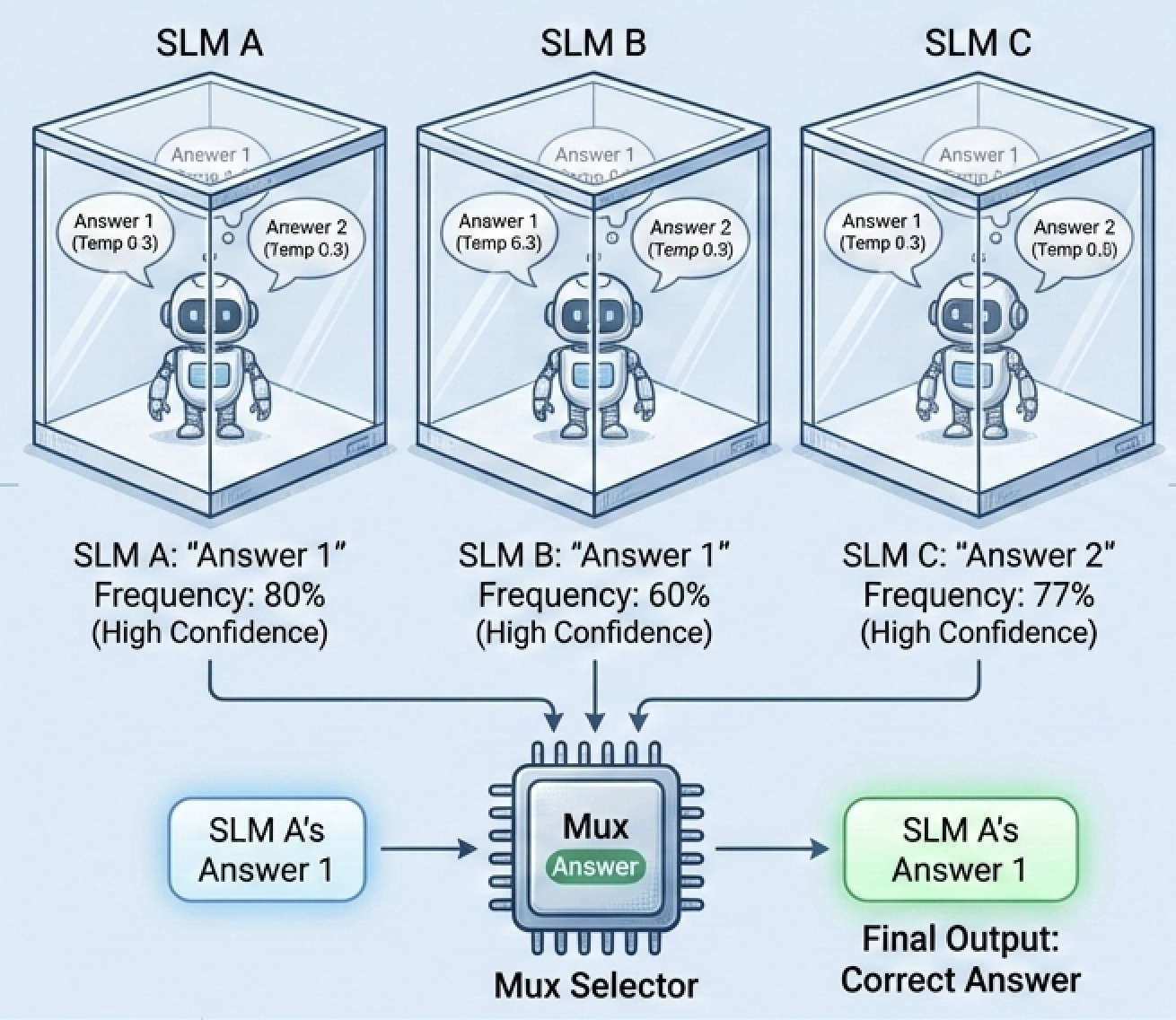

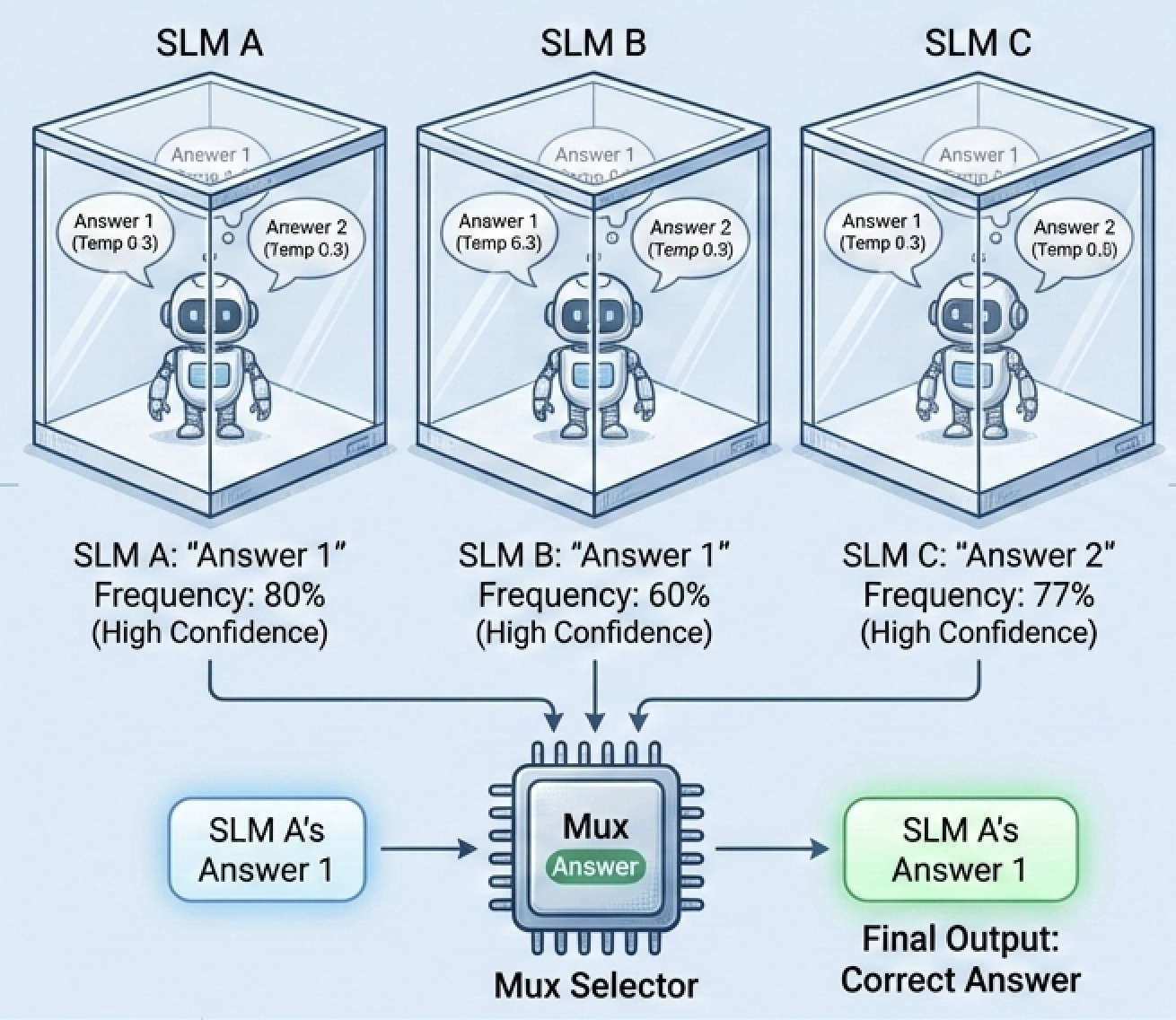

Chenyu Wang*, Zishen Wan*, Hao Kang, Emma Chen, Zhiqiang Xie, Tushar Krishna, Vijay Janapa Reddi, Yilun Du International Conference on Learning Representations (ICLR), 2026 Paper / Project Website / Code We propose SLM-Mux, a new multi-model framework to coordinate multiple smaller language models (SLMs) based on confidence and complementary strengths. SLM-MUX yields significant gains on reasoning benchmarks by optimizing model subsets and inference scaling. |

|

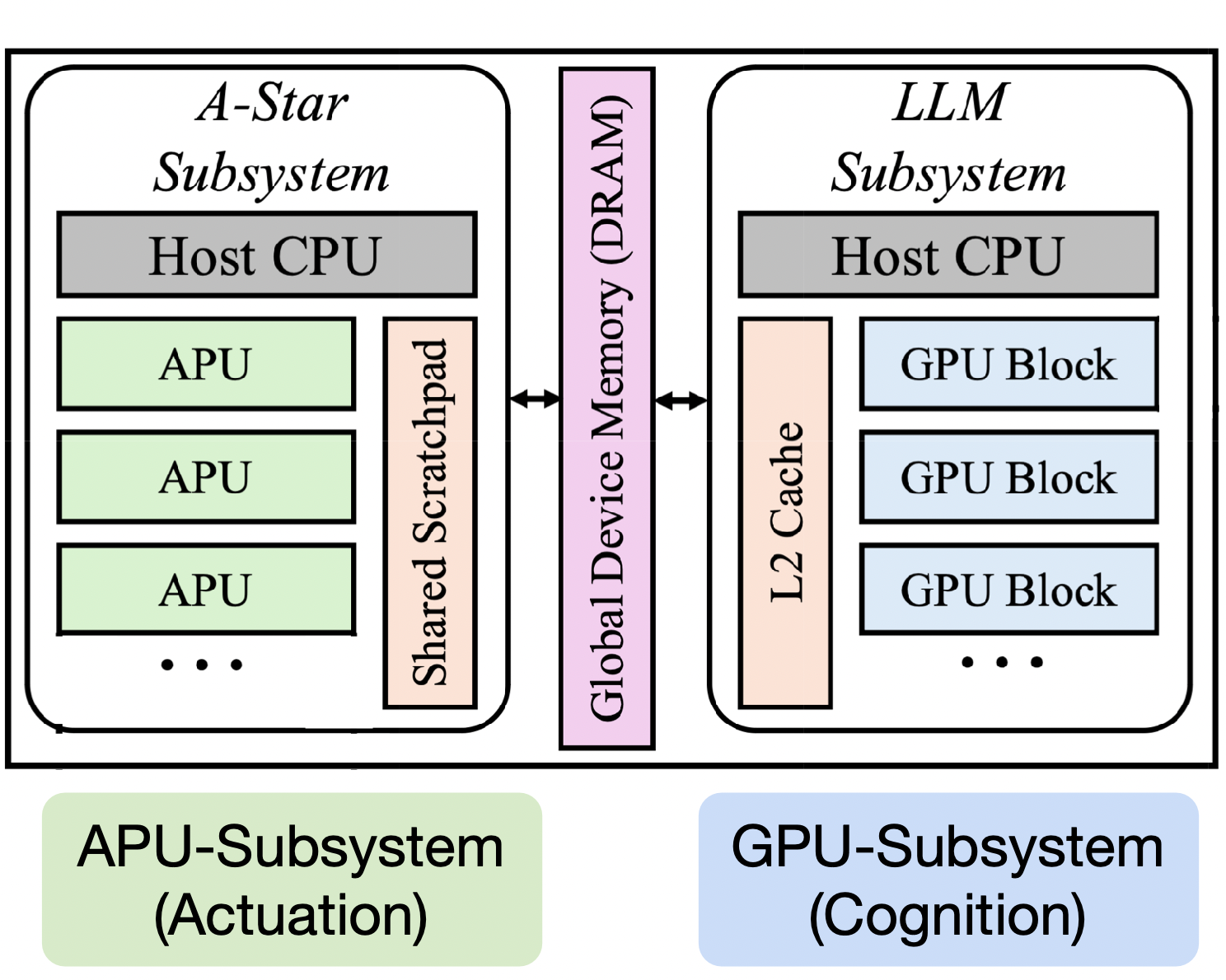

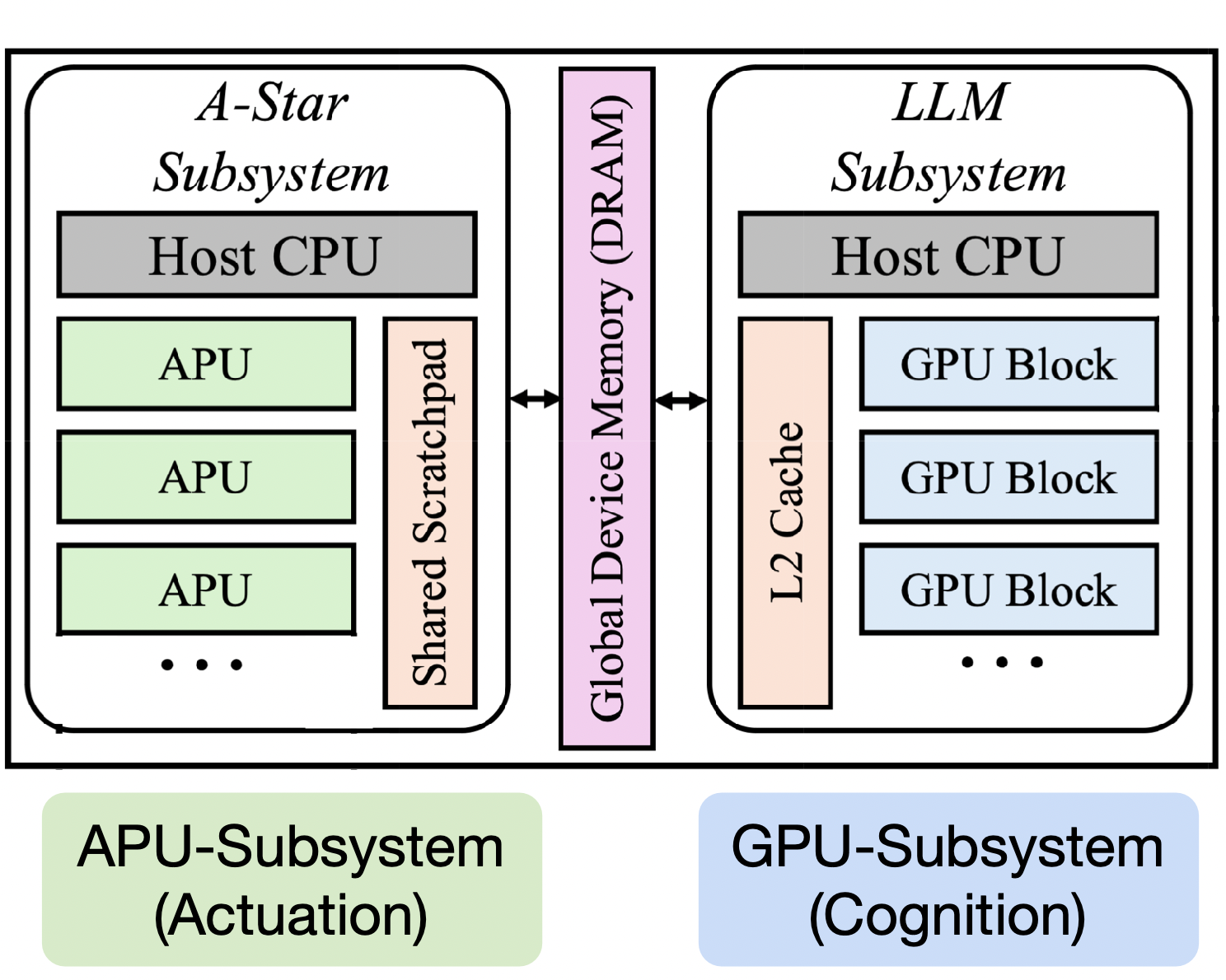

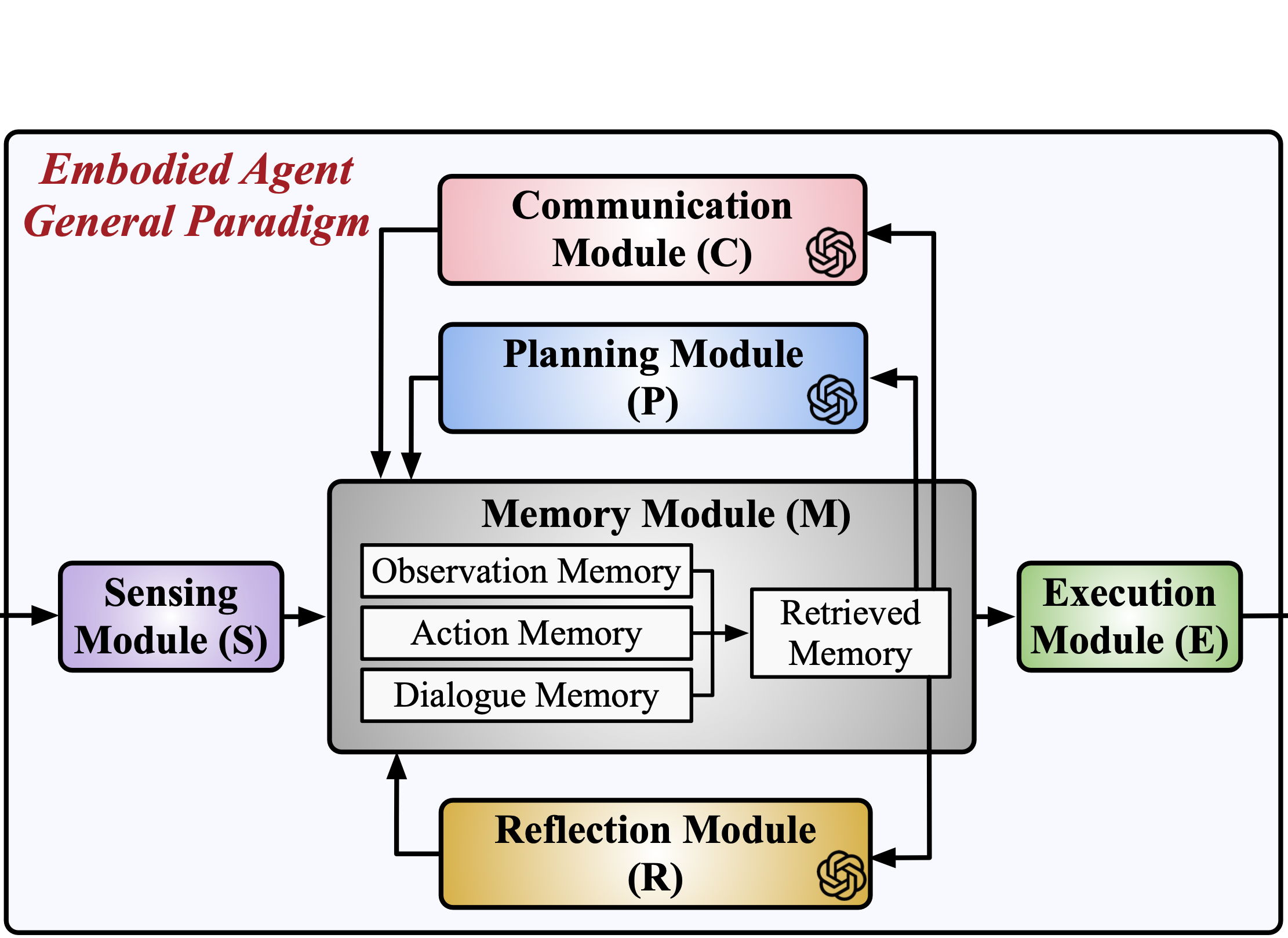

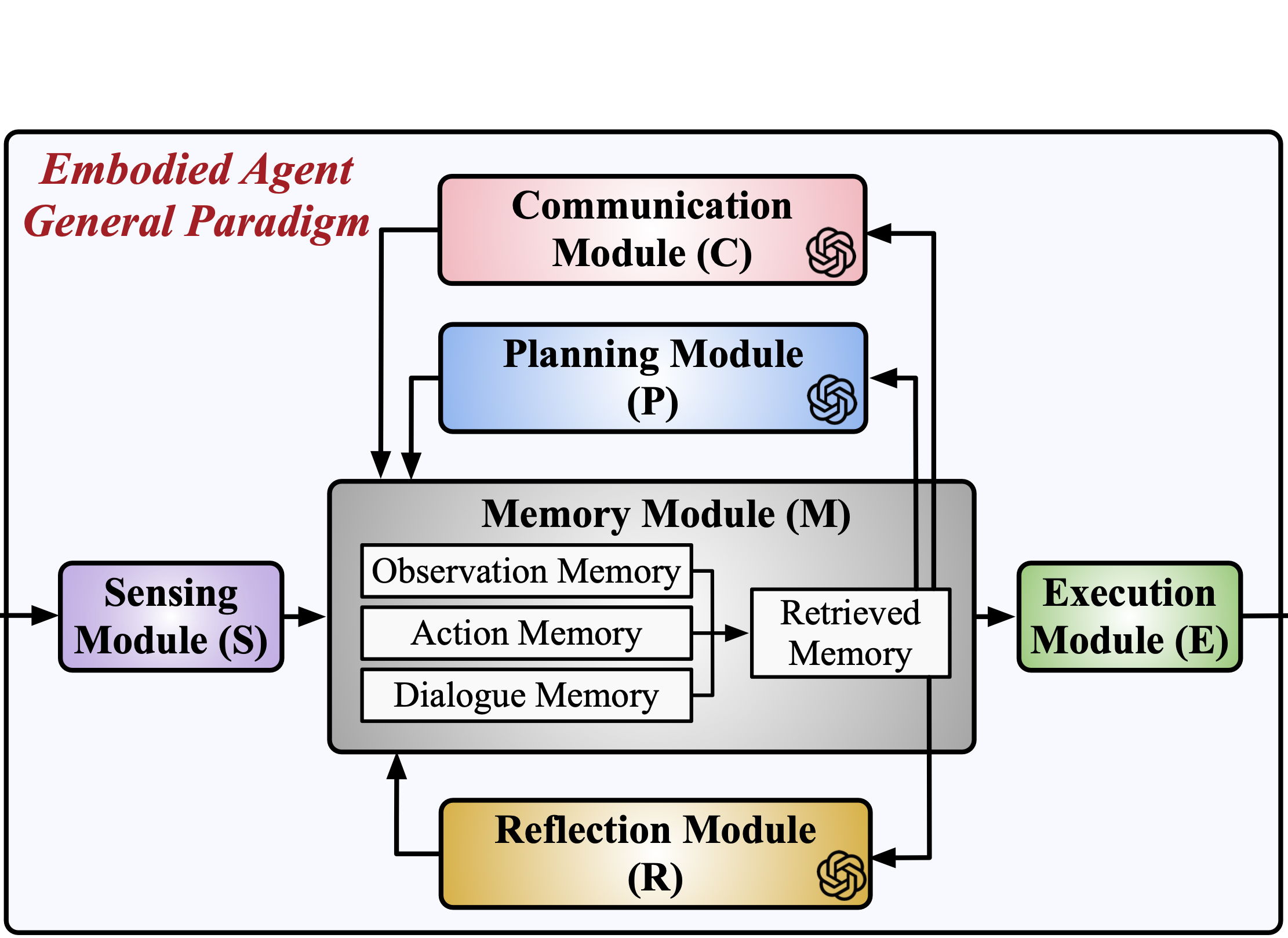

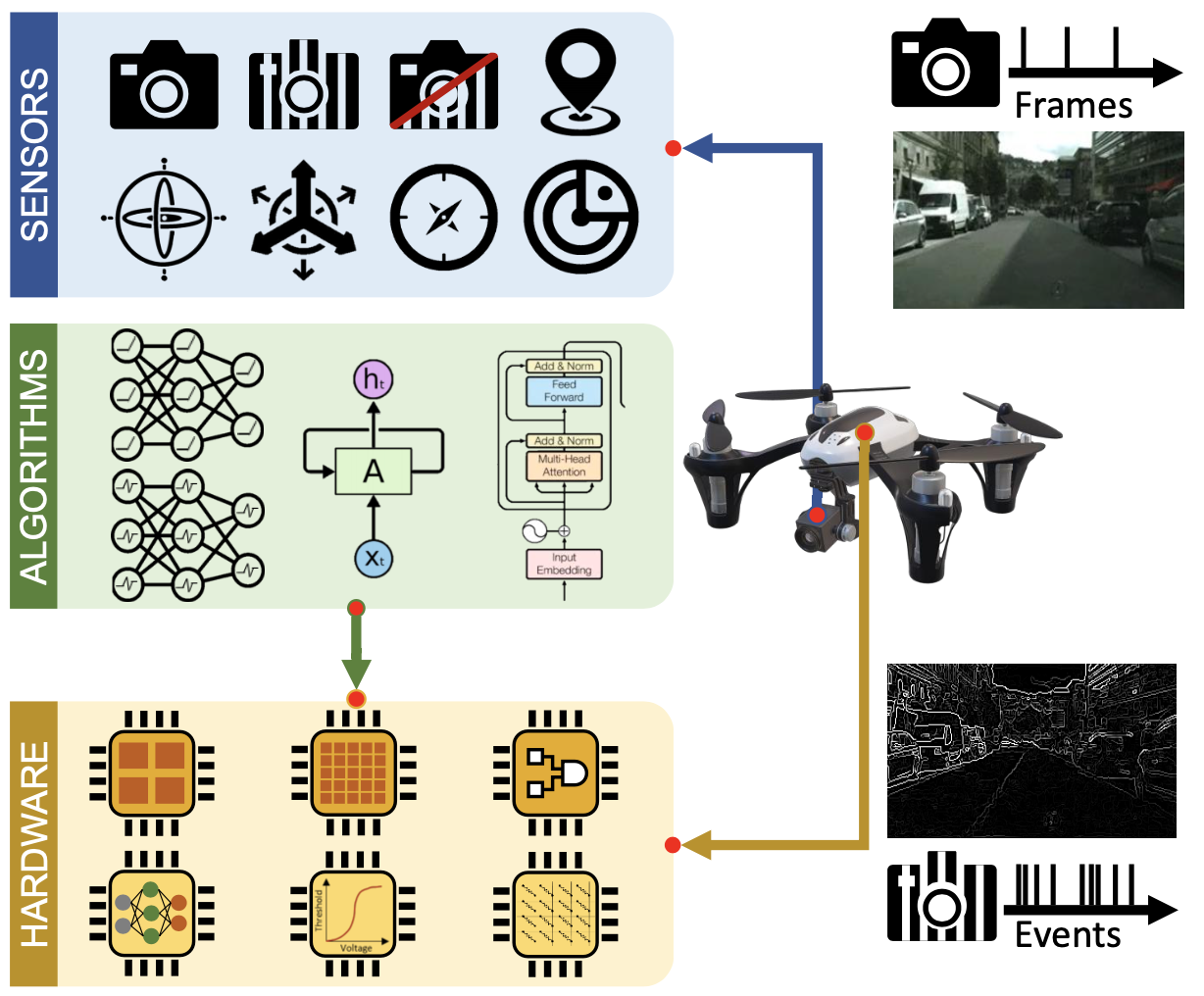

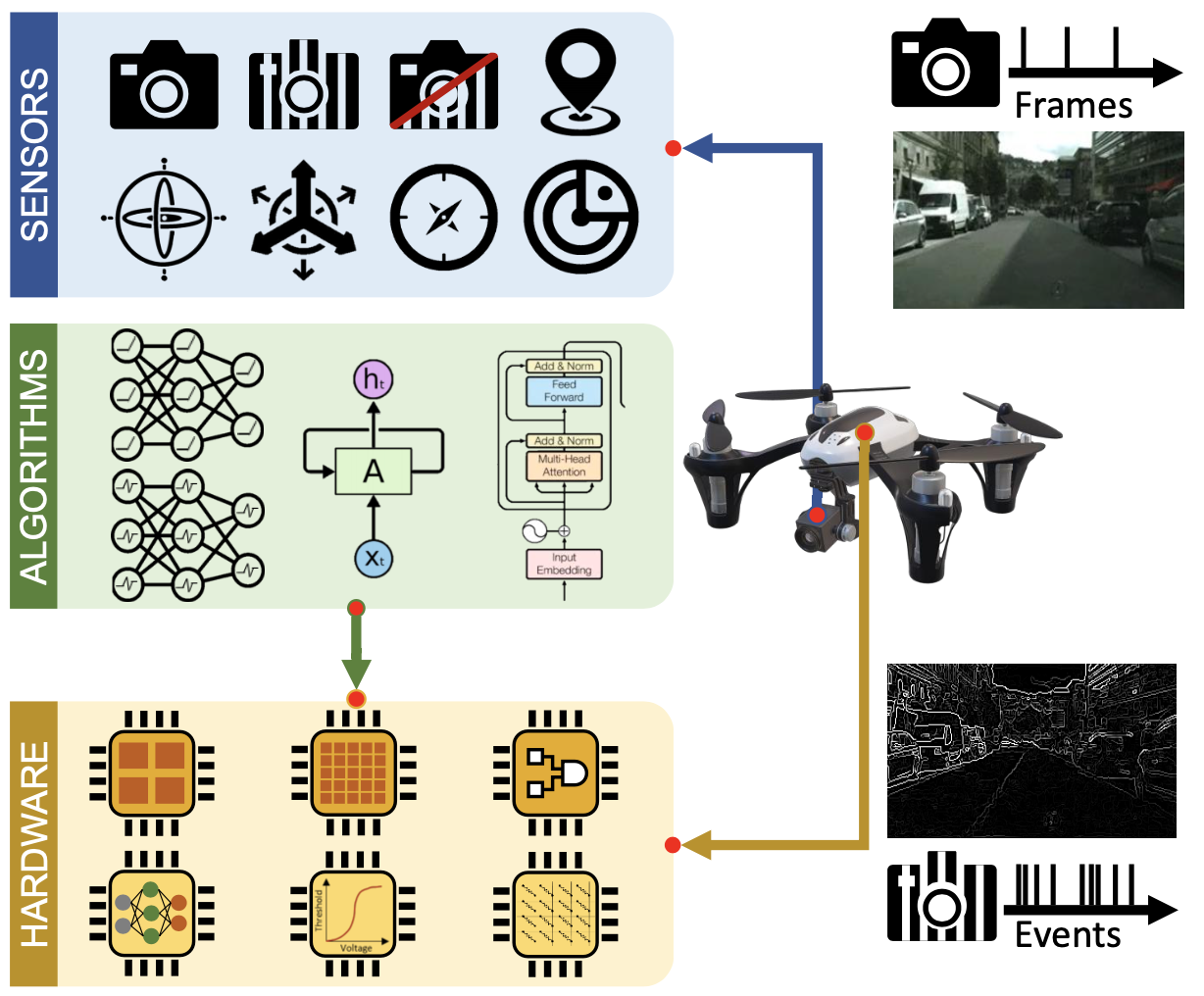

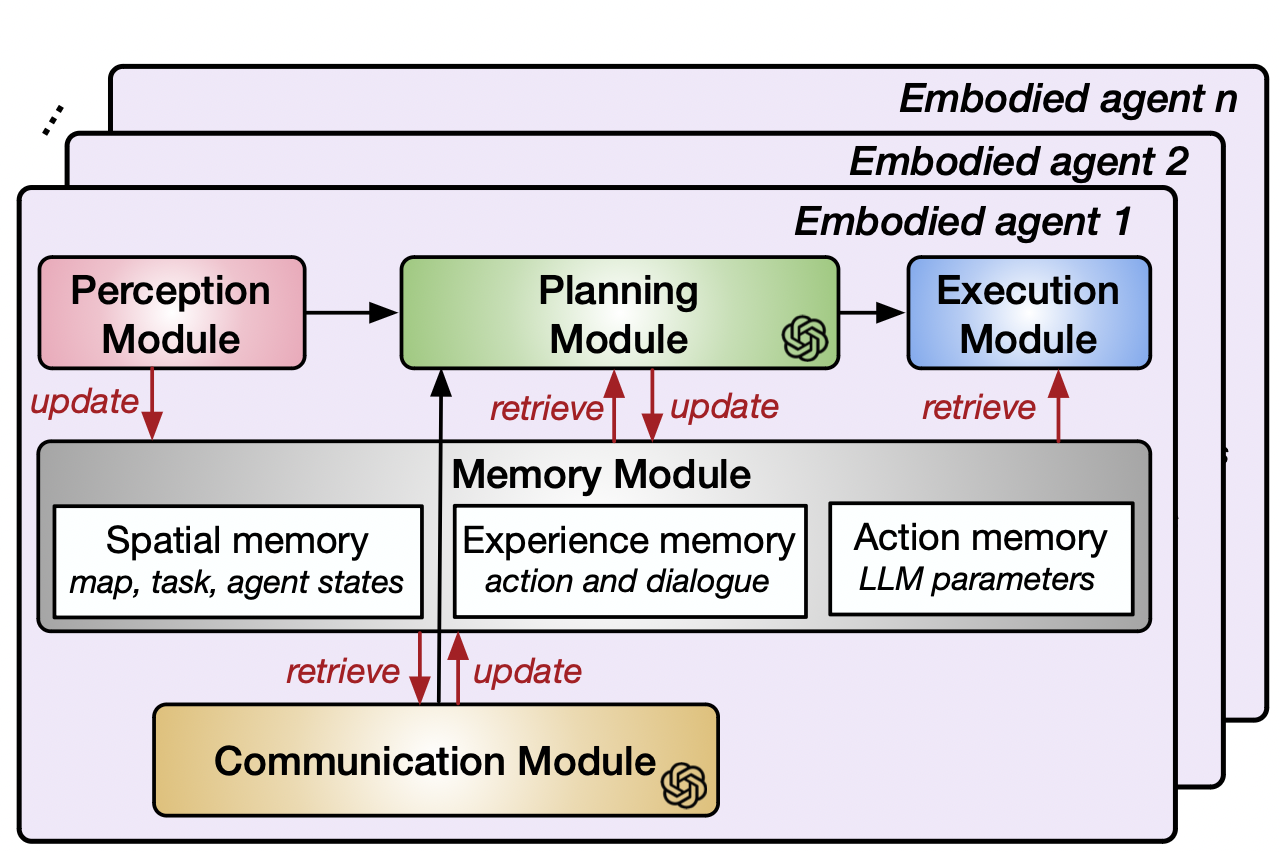

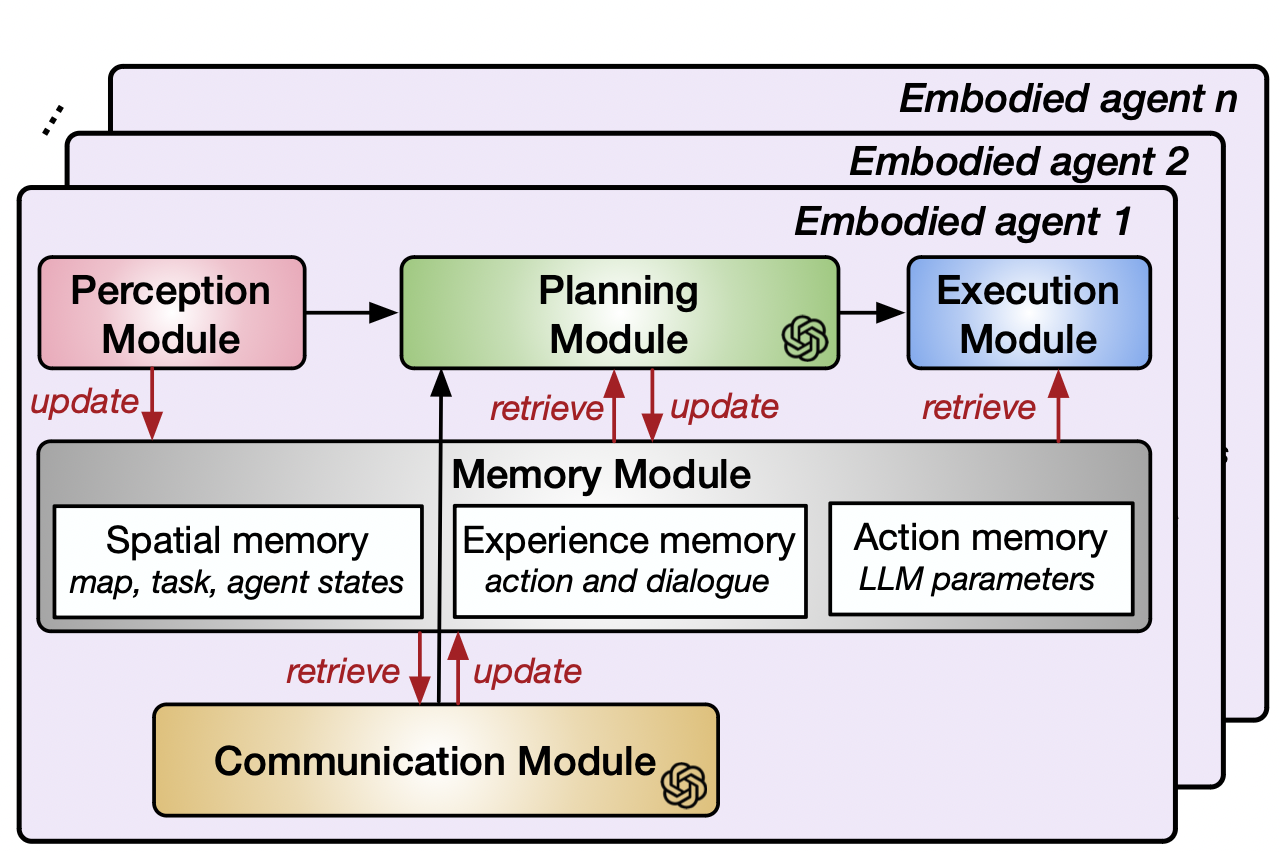

Zishen Wan, Yuhang Du, Mohamed Ibrahim, Jiayi Qian, Jason Jabbour, Yang (Katie) Zhao, Tushar Krishna, Arijit Raychowdhury, Vijay Janapa Reddi ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2025 Selected as Industry-Academia Partnership (IAP) Highlight Paper / Slide / Slide (long version) / Poster / Media We propose ReCA, a characterization and system-architecture co-design framework dedicated to cooperative embodied AI agent system acceleration, aiming to enhance both long-horizon multi-objective planning task efficiency and system scalability. |

|

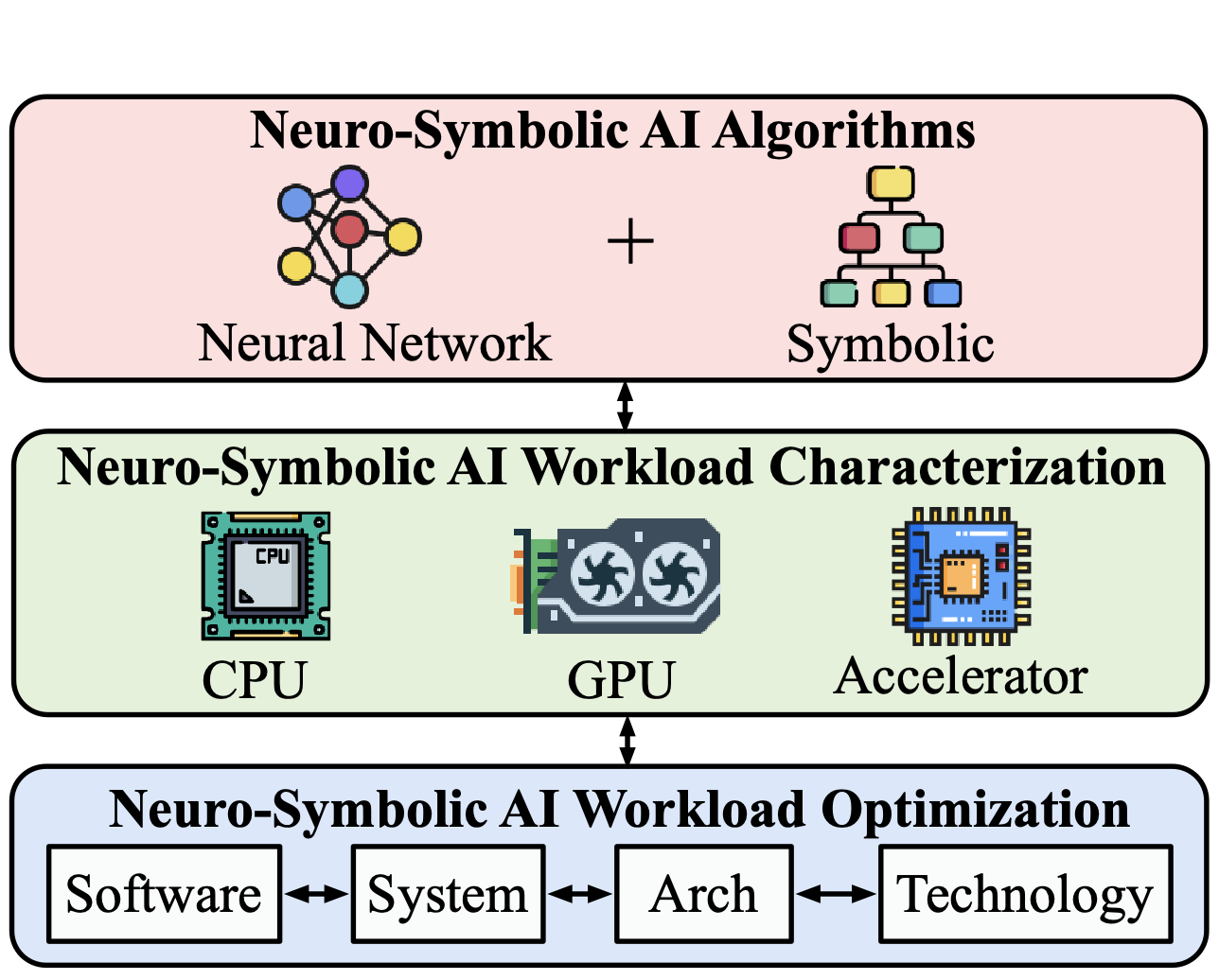

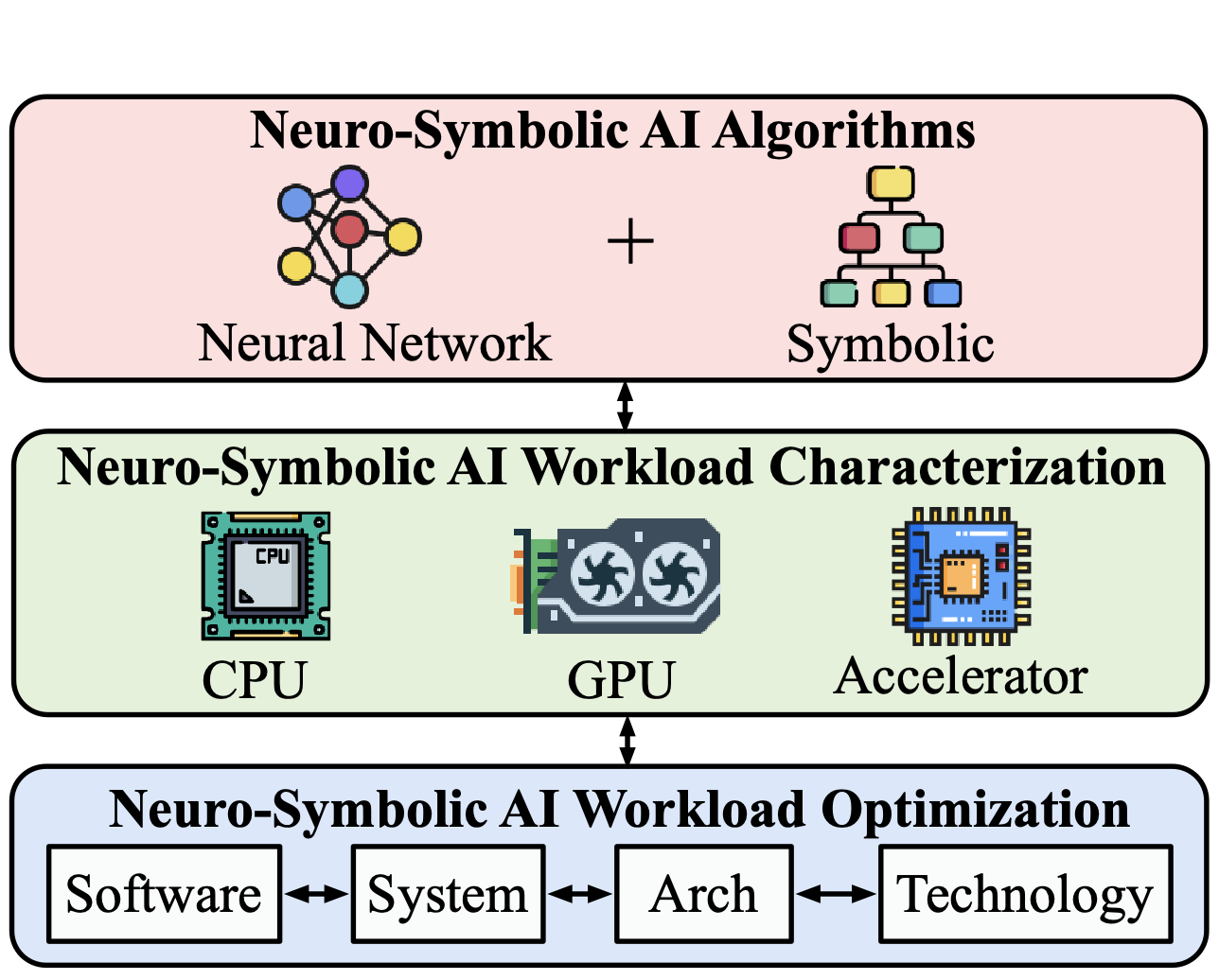

Zishen Wan*, Hanchen Yang*, Ritik Raj*, Che-Kai Liu, Ananda Samajdar, Arijit Raychowdhury, Tushar Krishna International Symposium on High-Performance Computer Architecture (HPCA), 2025 Best Paper Award, DARPA SRC JUMP 2.0, 2024 Paper / Project Website / Slide / Slide (long version) / Poster / Tutorial / Media We propose CogSys, a characterization and co-design framework dedicated to neurosymbolic AI system acceleration, aiming to win both reasoning efficiency and scalability. |

|

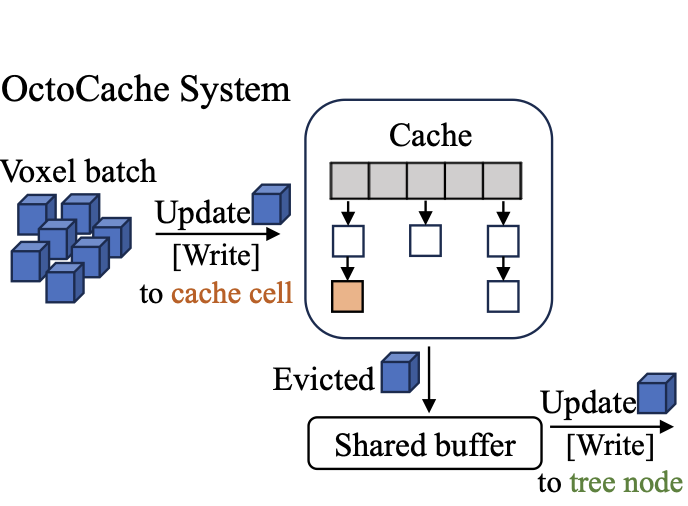

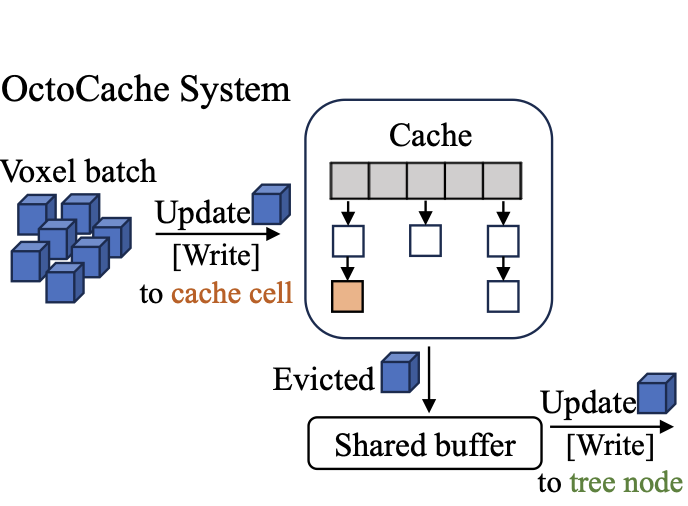

Peiqing Chen, Minghao Li, Zishen Wan, Yu-Shun Hsiao, Minlan Yu, Vijay Janapa Reddi, Zaoxing (Alan) Liu ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2025 Paper We propose OctoCache, a software system designed to accelerate 3D occupancy mapping performance in autonomous systems. OctoCache improves mapping system update speed through three mechanisms: (1) optimization of cache memory access, (2) refinement of voxel ordering, and (3) workflow parallelization. |

|

Leshu Li, Jiayin Qin, Jie Peng, Zishen Wan, Huaizhi Qu, Ye Han, Pingqing Zheng, Hongsen Zhang, Yu (Kevin) Cao, Tianlong Chen, Yang (Katie) Zhao ACM/IEEE International Symposium on Microarchitecture (MICRO), 2025 Paper / Code We propose RTGS, an algorithm-hardware co-designed framework that enables real-time 3D Gaussian Splatting SLAM on edge devices by reducing multi-level computational redundancies. RTGS achieves real-time rendering performance through adaptive pruning, dynamic downsampling, and a GPU-integrated design. |

|

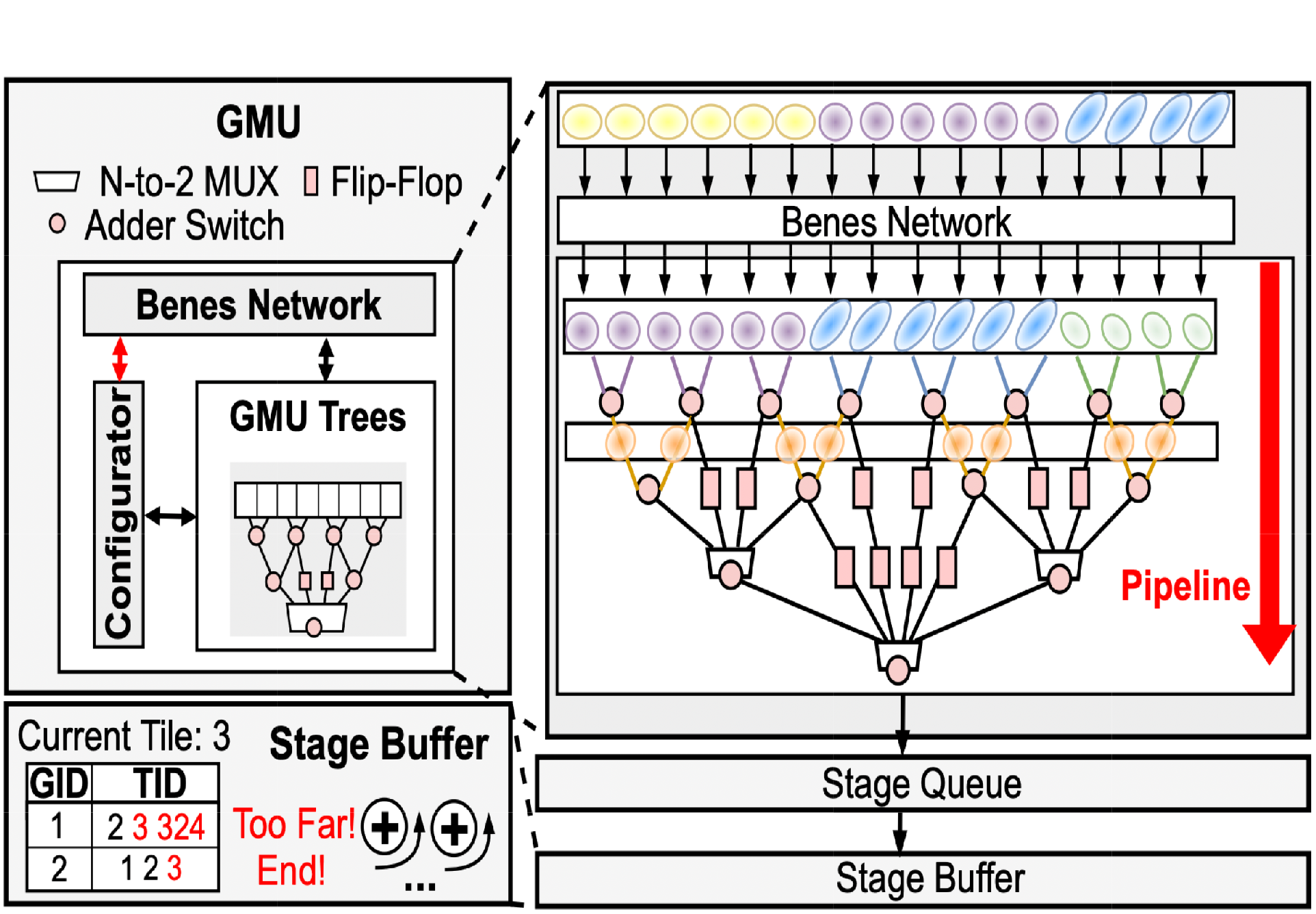

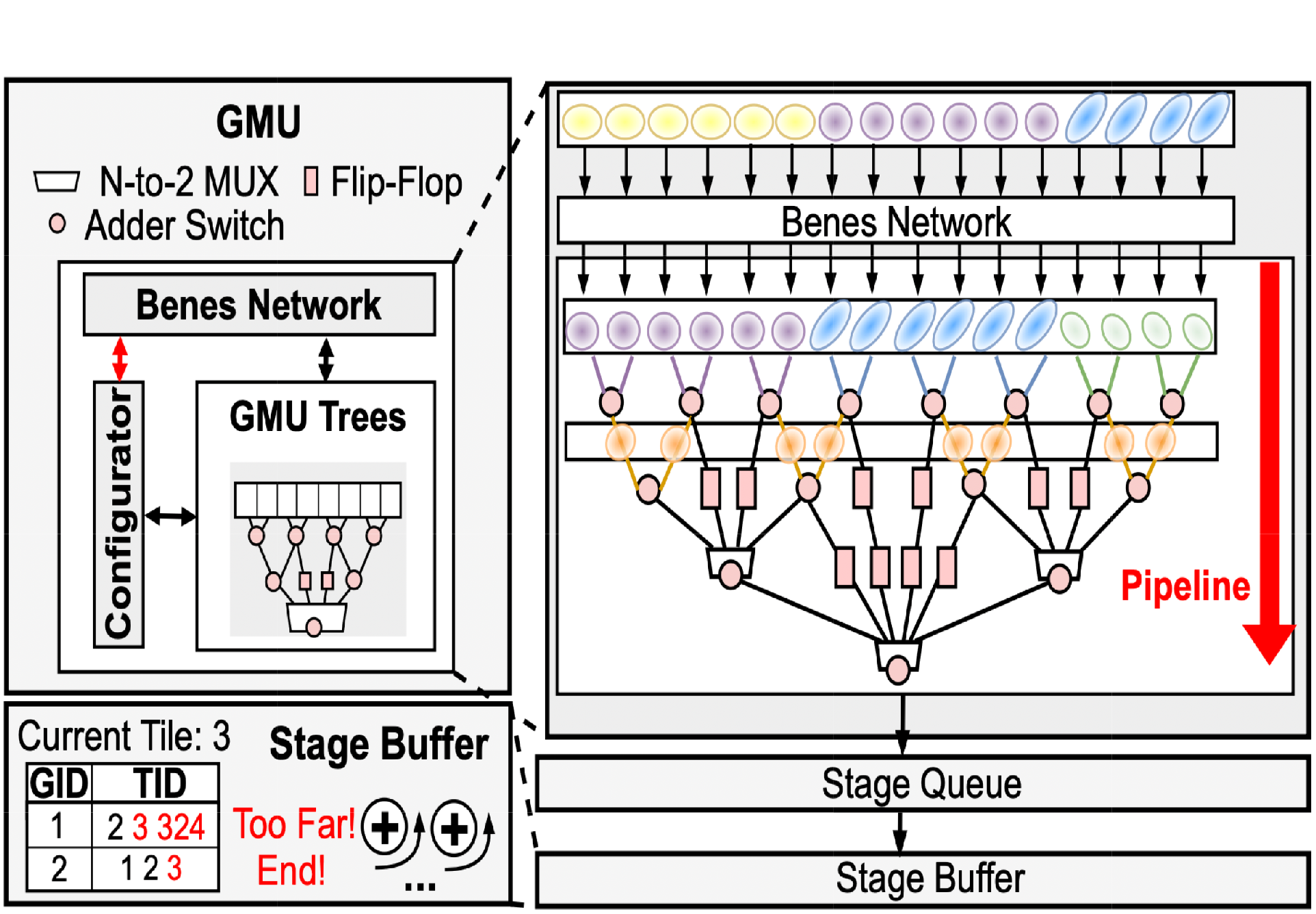

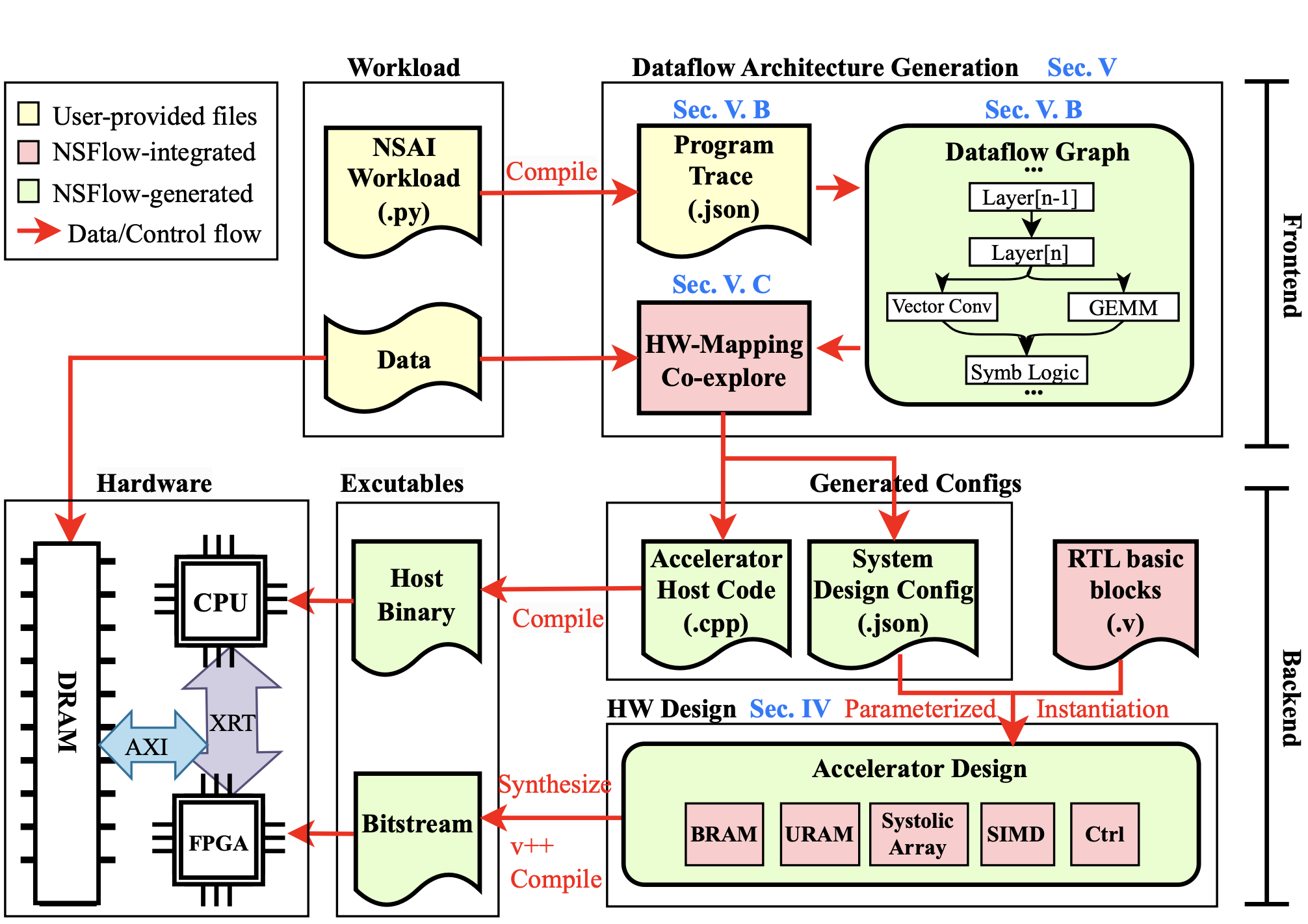

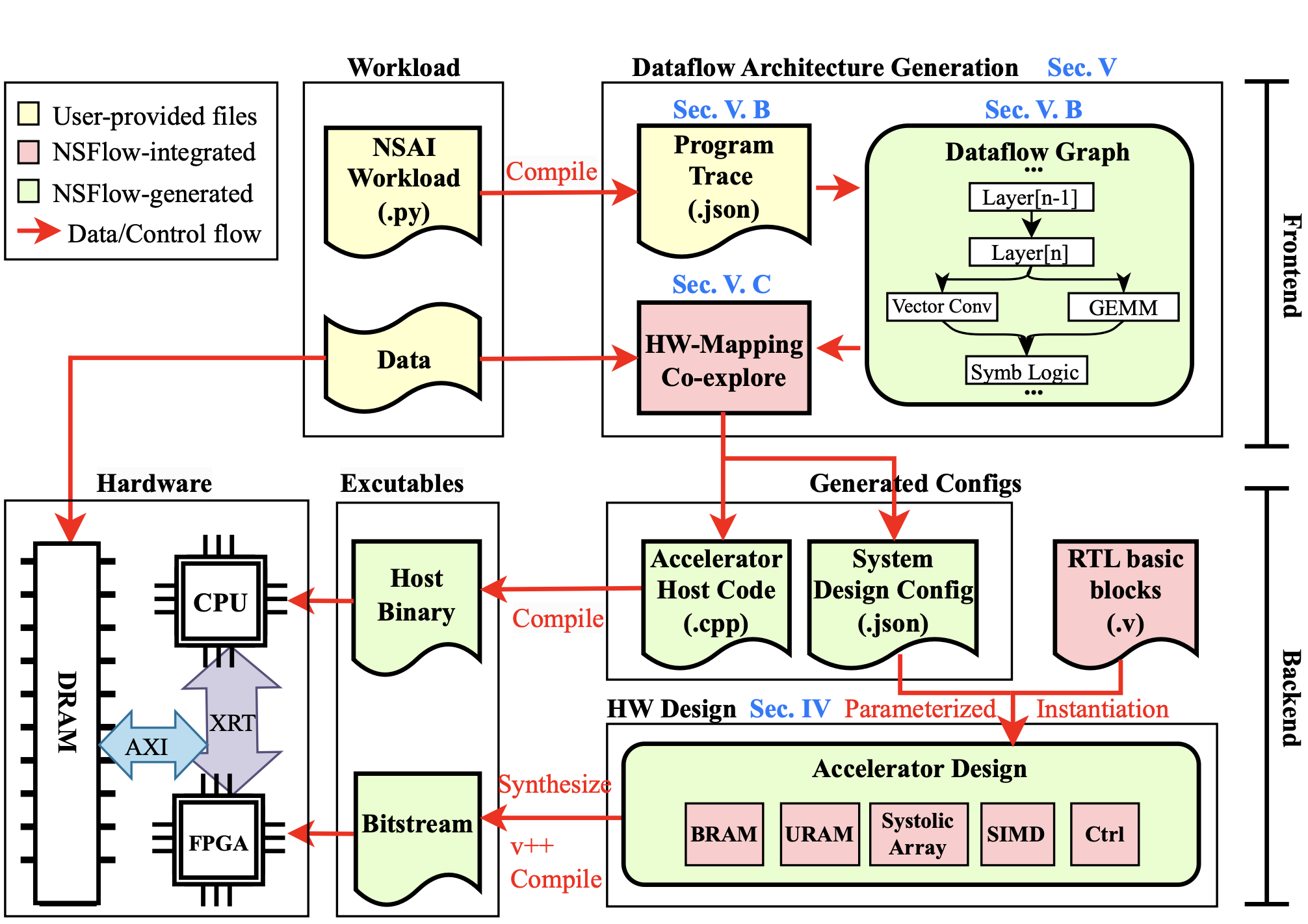

Hanchen Yang*, Zishen Wan*, Ritik Raj, Joongun Park, Ziwei Li, Ananda Samajdar, Arijit Raychowdhury, Tushar Krishna ACM/IEEE Design Automation Conference (DAC), 2025 Paper / Slide We propose NSFlow, an FPGA framework for efficient, scalable, and adaptive across neuro-symbolic systems. NSFlow features a design architecture generator that identifies workload data dependencies and creates dataflow architectures, as well as reconfigurable array with flexible compute units and re-organizable memory. |

|

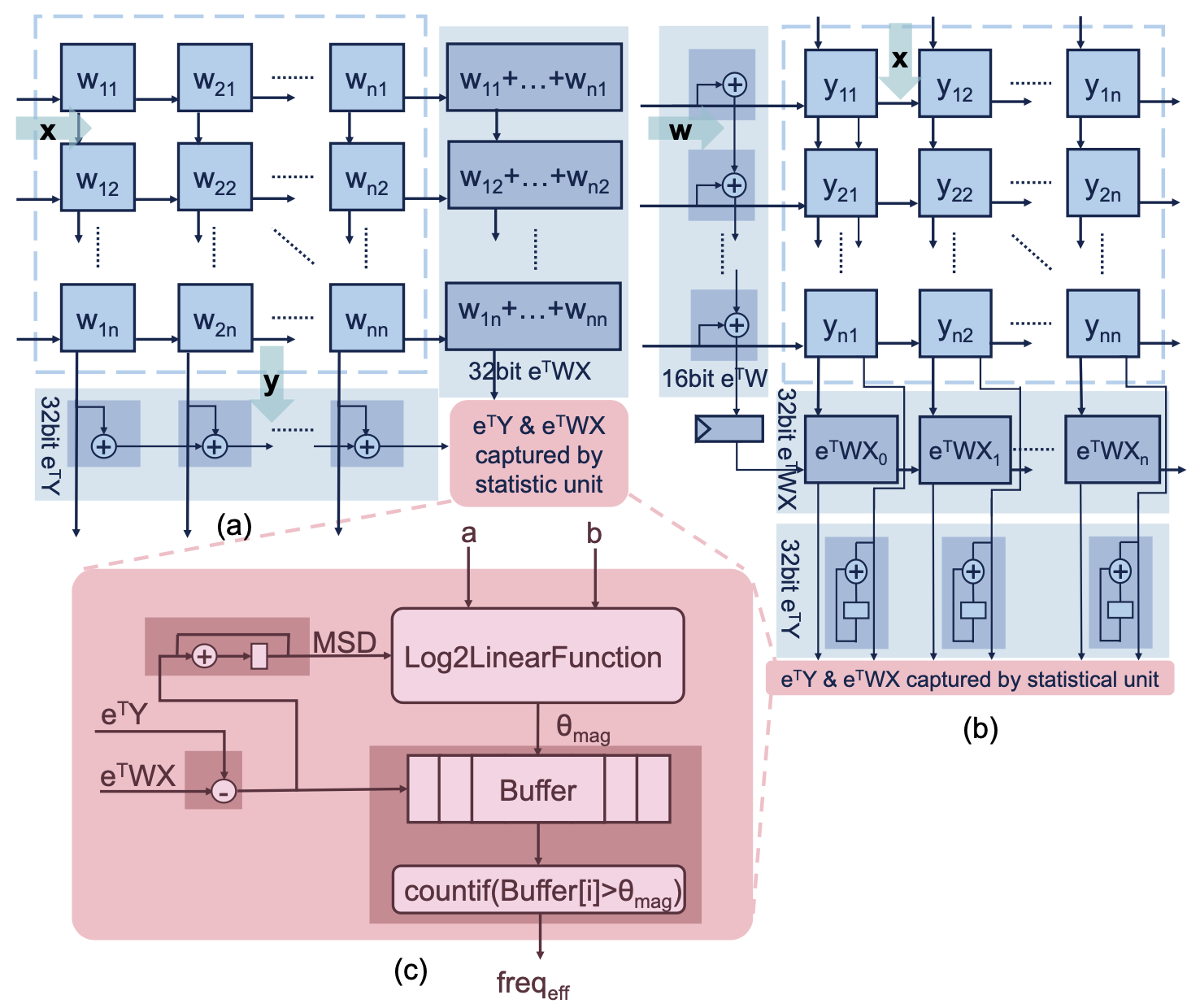

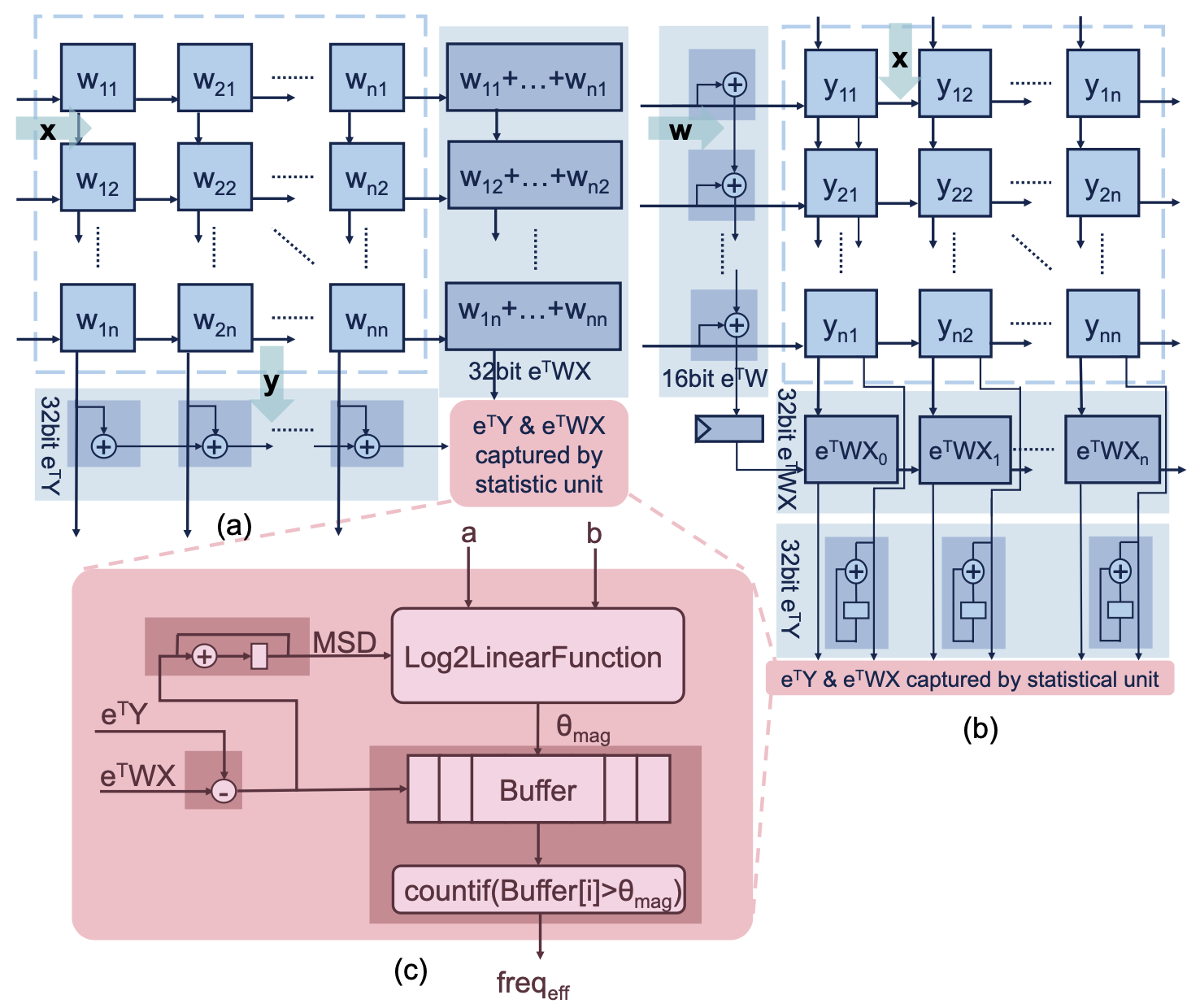

Tong Xie, Jiawang Zhao, Zishen Wan, Zuodong Zhang, Yuan Wang, Runsheng Wang, Ru Huang, Meng Li ACM/IEEE Design Automation Conference (DAC), 2025 Paper / Code We propose ReaLM, an algorithm/circuit co-design framework for resilient and efficient LLM inference. ReaLM systematically characterizes the fault tolerance of LLMs, and introduces a statistical algorithm-based fault tolerance algorithm and error detection circuit to enable cost-effective fault detection and mitigation for LLMs. |

|

Zishen Wan, Jiayi Qian, Yuhang Du, Jason Jabbour, Yilun Du, Yang (Katie) Zhao, Arijit Raychowdhury, Tushar Krishna, Vijay Janapa Reddi IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2025 Paper / Slide This paper systematically categorizes the workload characteristics of embodied agent systems and presents a benchmark suite to evaluate their task performance and system efficiency, suggests system optimization strategies to improve the performance, efficiency, and scalability of future embodied system design. |

|

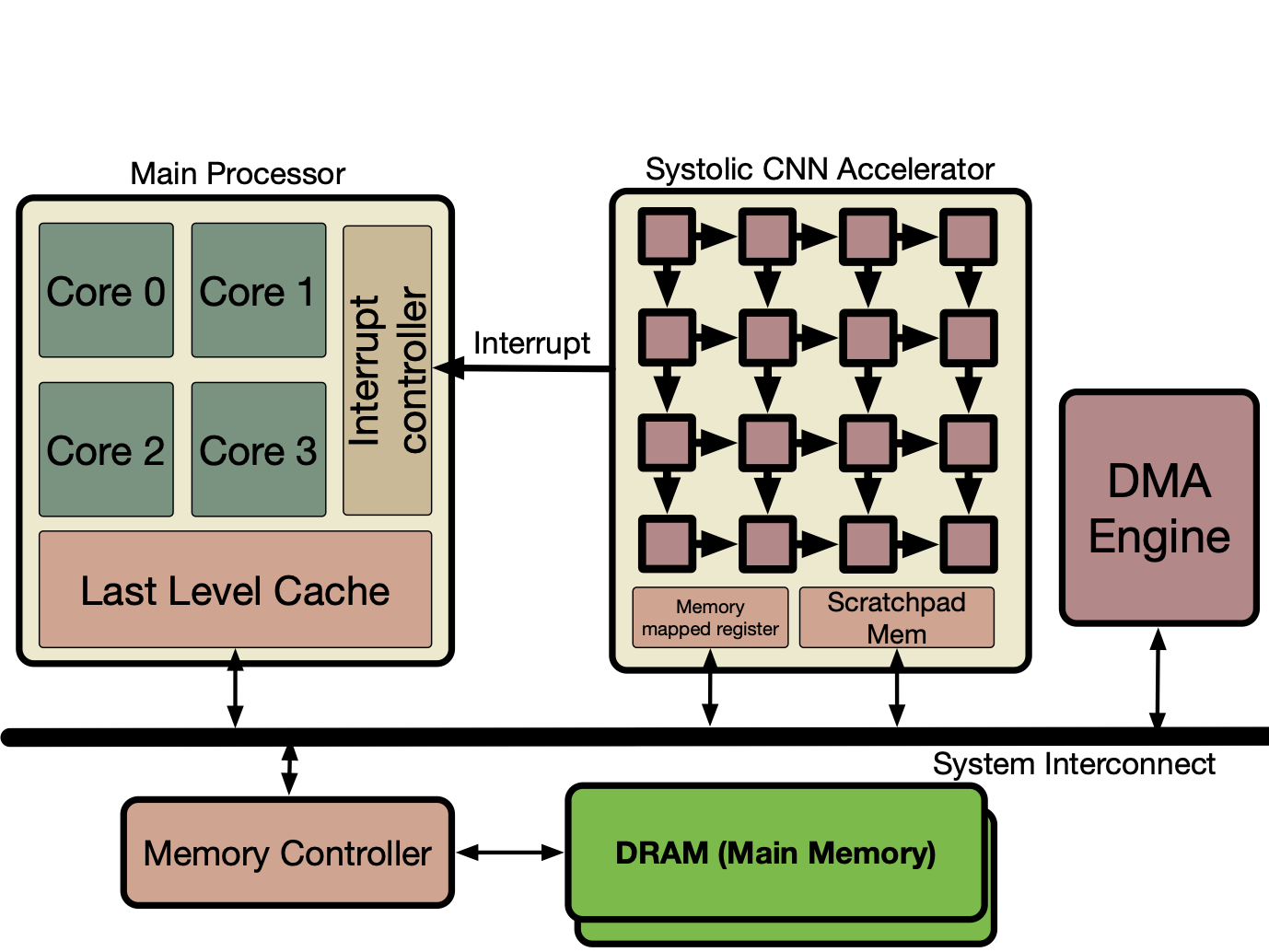

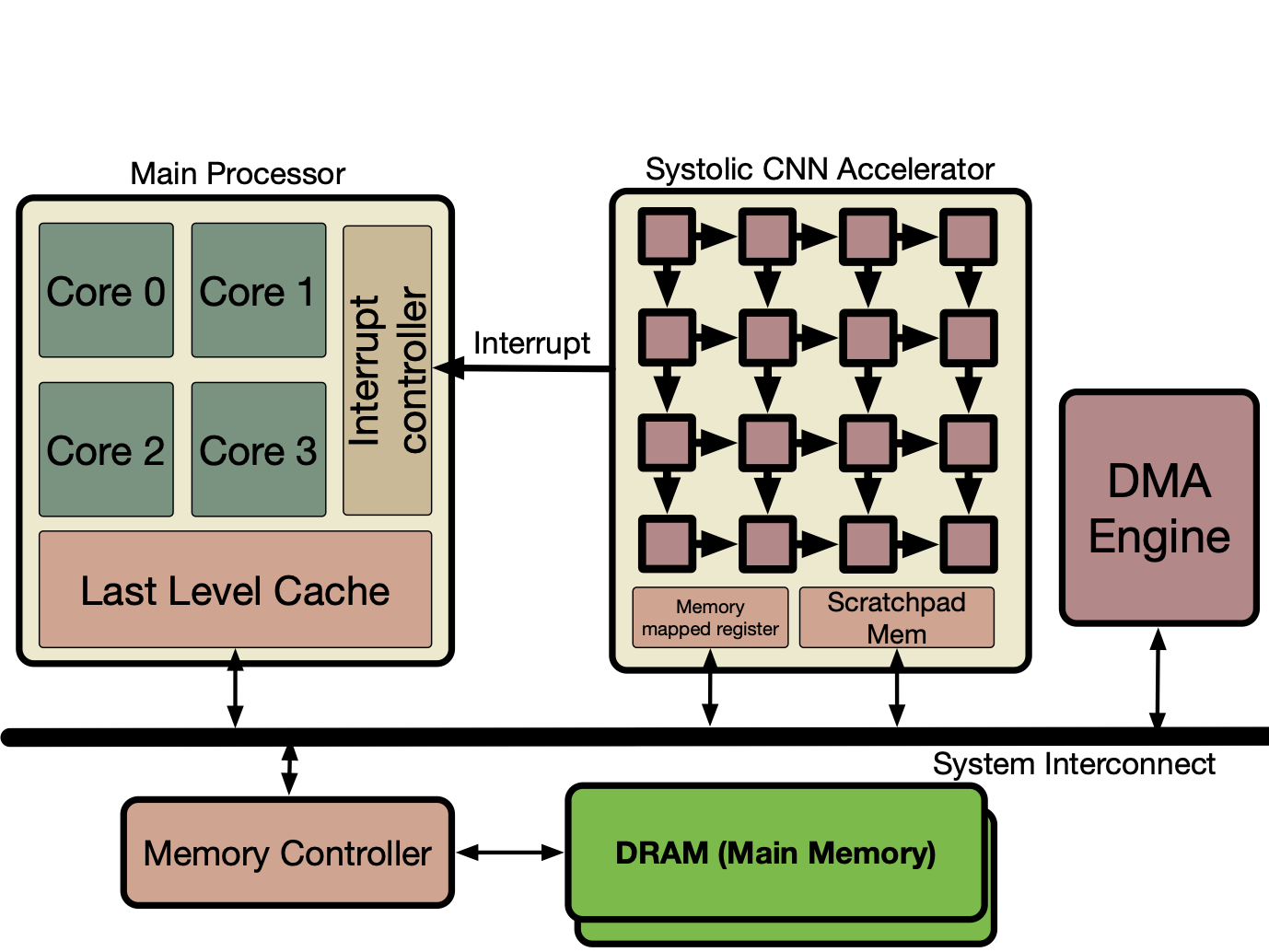

Ritik Raj, Sarbartha Banerjee*, Nikhil Srinivas*, Zishen Wan*, Jianming Tong*, Ananda Samajdar, Tushar Krishna IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2025 Paper / Code We present SCALE-Sim v3, a modular cycle-accurate simulator for systolic-array-based architectures, featuring multi-core architecture with spatio-temporal partitioning, sparsity, DRAM ramulator, precise data layout modeling, and energy and power estimation via Accelergy. |

|

Kaushik Roy, Adarsh Kosta, Tanvi Sharma, Shubham Negi, Deepika Sharma, Utkarsh Saxena, Sourjya Roy, Anand Raghunathan, Zishen Wan, Samuel Spetalnick, Che-Kai Liu, Arijit Raychowdhury Frontiers in Science, 2025 Paper / Media This perspective paper highlights the challenges and research opportunities posed by ever-growing AI models and explores brain-inspired algorithms, novel memory technologies, and algorithm–hardware co-design strategies for building efficient, sustainable, and edge-ready AI systems. |

|

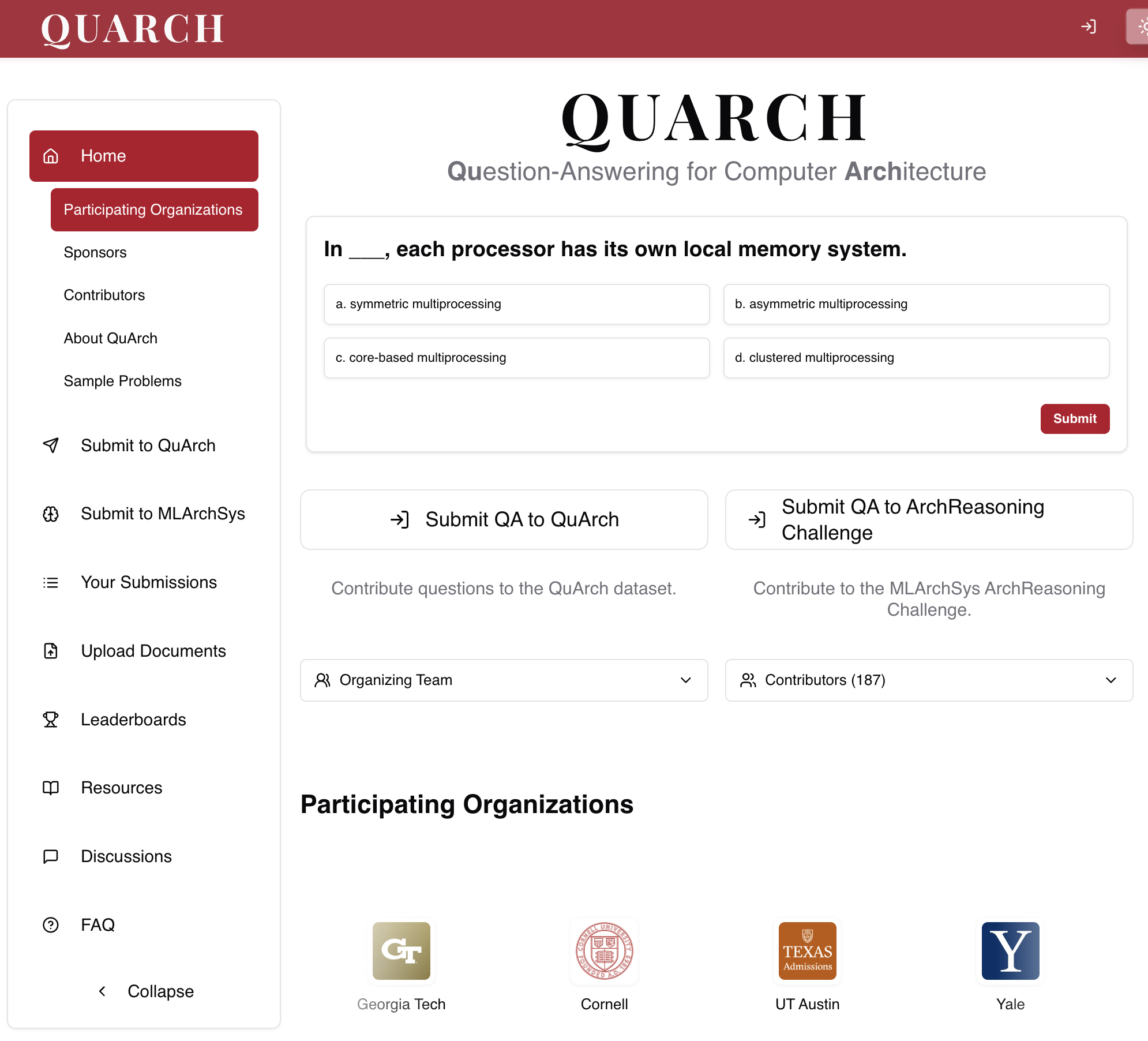

Shvetank Prakash, Andy Cheng, Arya Tschand, Mark Mazumder, Varun Gohil, Jeff Ma, Jason Yik, Zishen Wan, Jessica Quaye, Elisavet Lydia Alvanaki, Avinash Kumar, Chandrashis Mazumdar, Tuhin Khare, Alexander Ingare, Ikechukwu Uchendu, Radhika Ghosal, Abhishek Tyagi, Chenyu Wang, Andrea Mattia Garavagno, Sarah Gu, Alice Guo, Grace Hur, Luca Carloni, Tushar Krishna, Ankita Nayak, Amir Yazdanbakhsh, Vijay Janapa Reddi arXiv Preprint, 2025 Paper / Project Website We propose QuArch, a benchmark of 2671 expert-validated Q&A pairs for evaluating LLMs’ reasoning and domain knowledge in computer architecture. While current LLMs grasp basic architectural knowledge, they still struggle significantly on higher-order reasoning tasks.. |

|

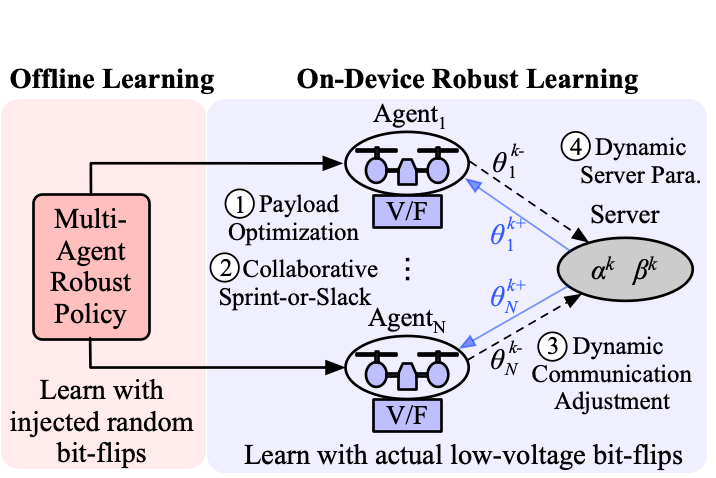

Zishen Wan, Nandhini Chandramoorthy, Karthik Swaminathan, Pin-Yu Chen, Kshitij Bhardwaj, Vijay Janapa Reddi, Arijit Raychowdhury ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2024 Best Poster Award, IBM IEEE AI Compute Symposium 2023 Paper / Slide / Poster / Lightning Talk / Media We propose MulBERRY, a multi-agent robust learning framework to enhance bit error robustness and energy efficiency for autonomous swarm systems. |

|

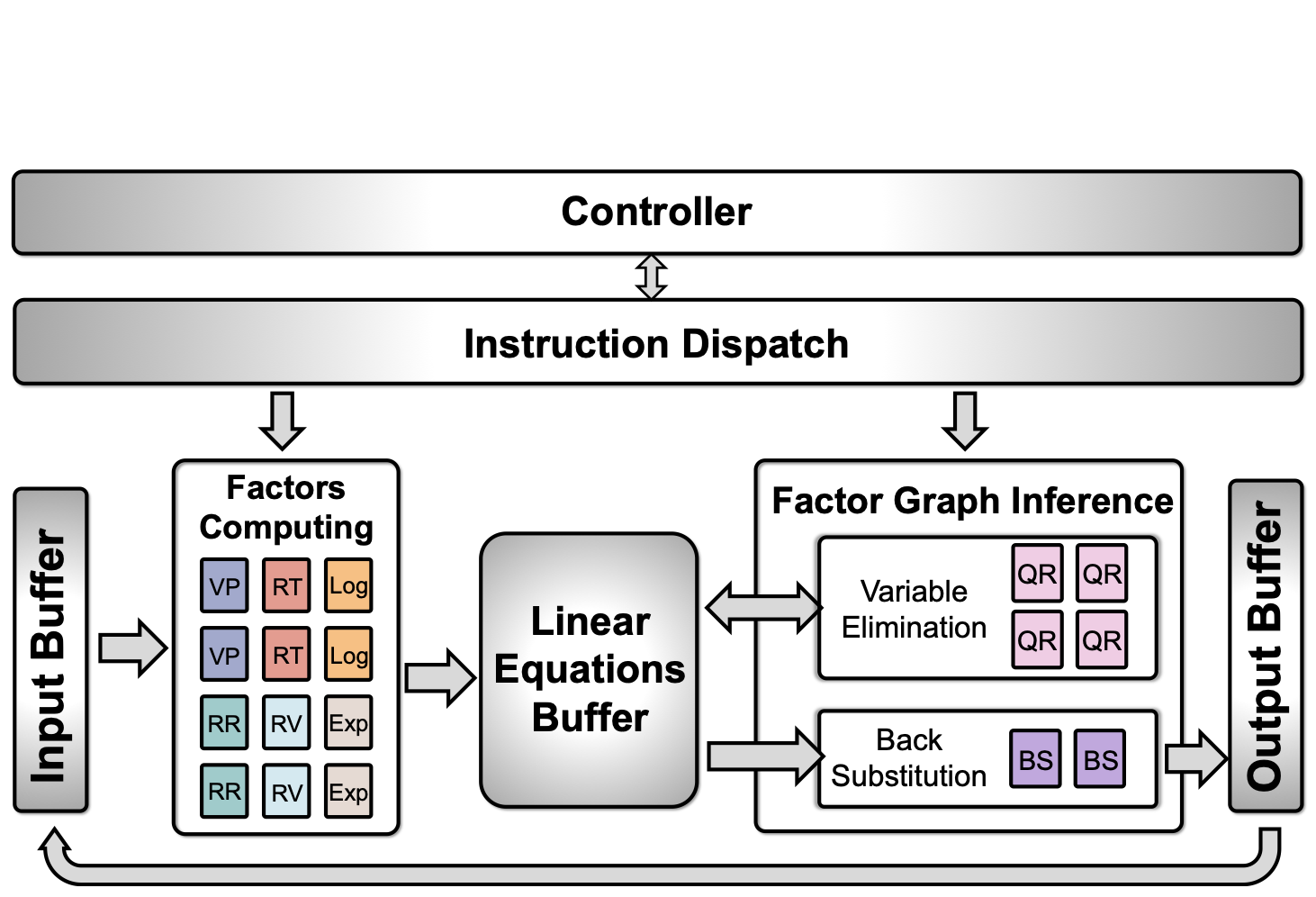

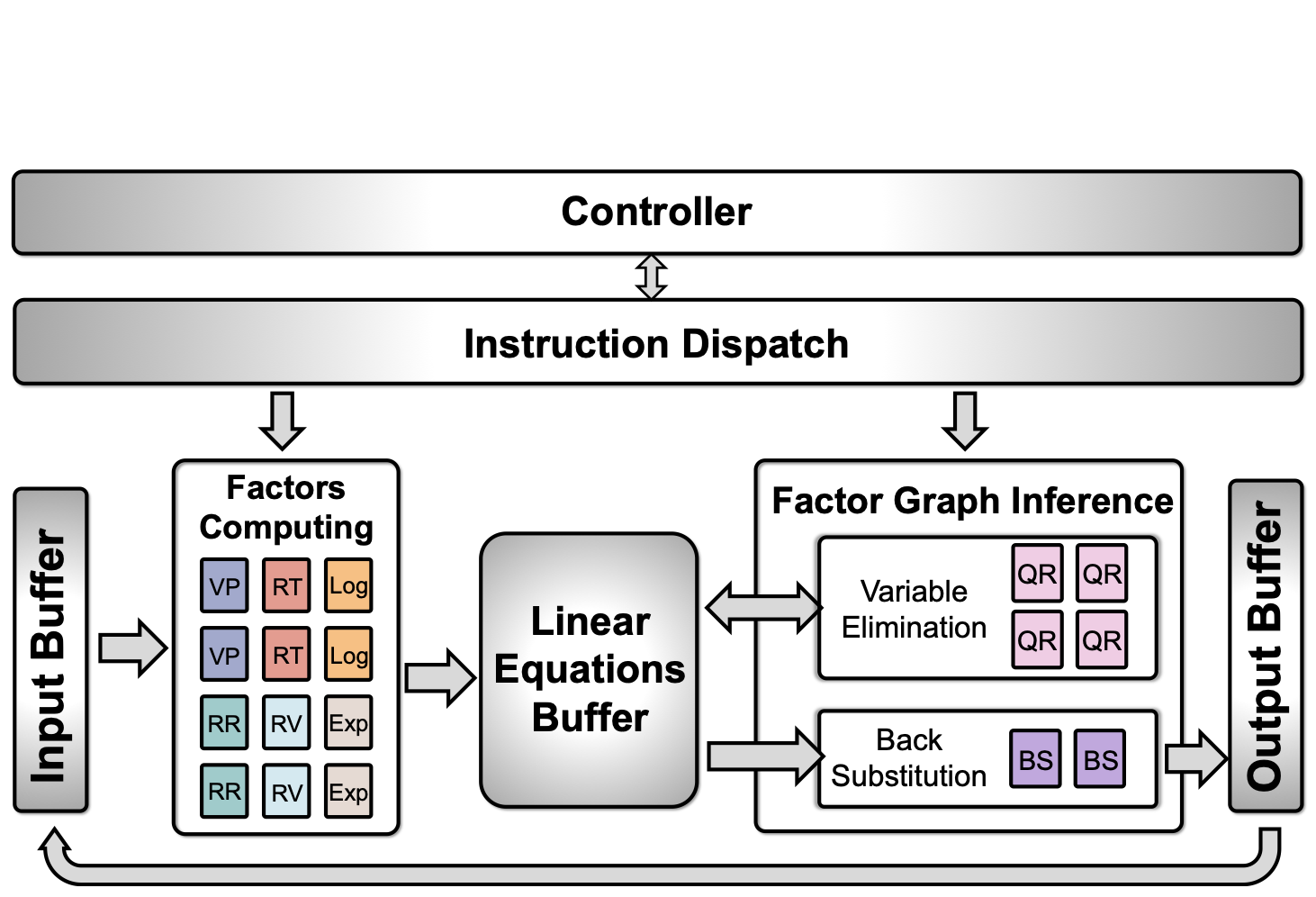

Yuhui Hao, Yiming Gan, Bo Yu, Qiang Liu, Yinhe Han, Zishen Wan, Shaoshan Liu ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2024 Paper / Lightning Talk / Poster We propose ORIANNA, a framework leverageing a common abstraction factor graph to generate accelerators for diverse robotic applications (e.g., manipulators, vehicles, drones) containing multiple optimization-based algorithms (e.g., localization, planning). |

|

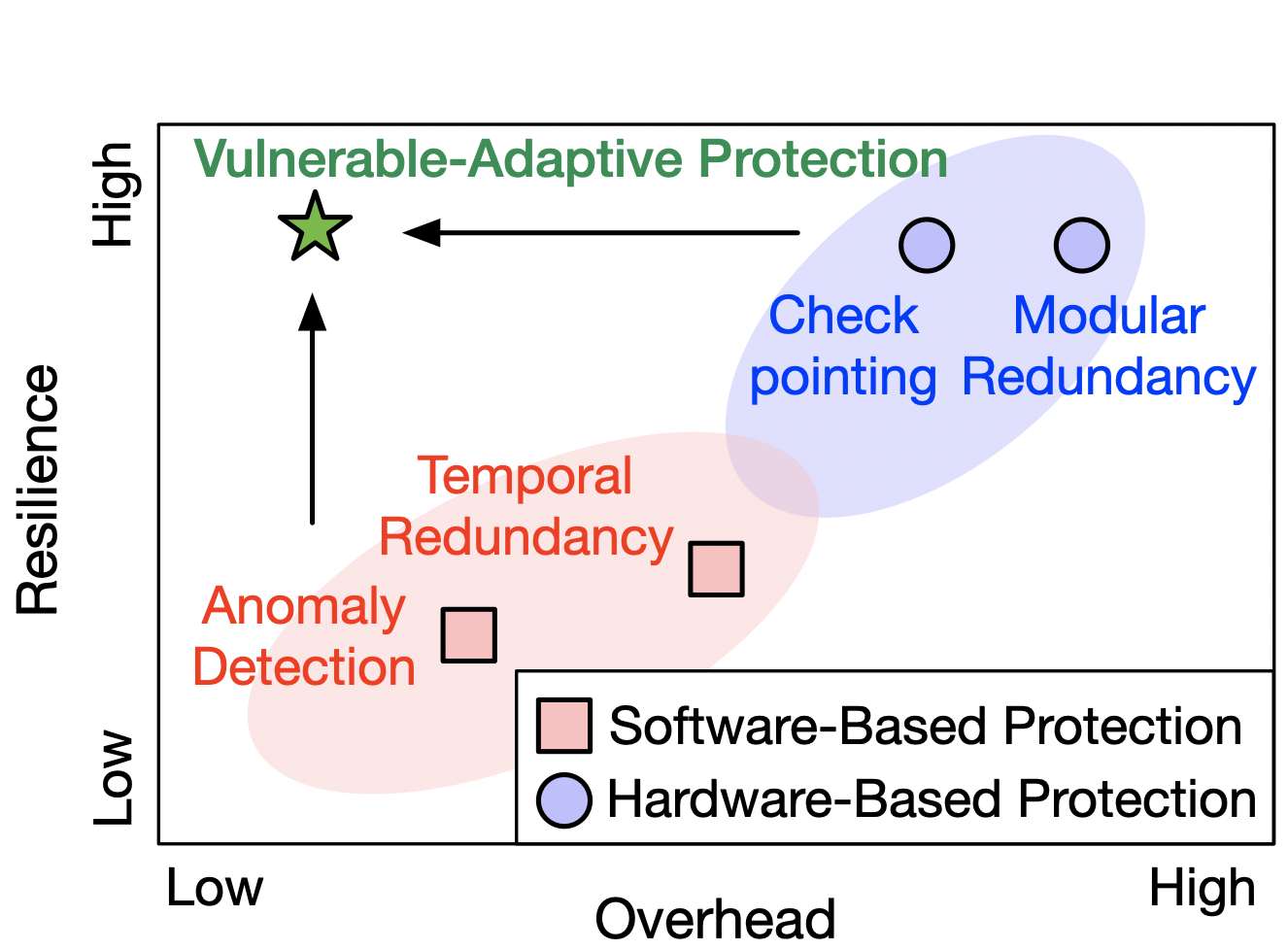

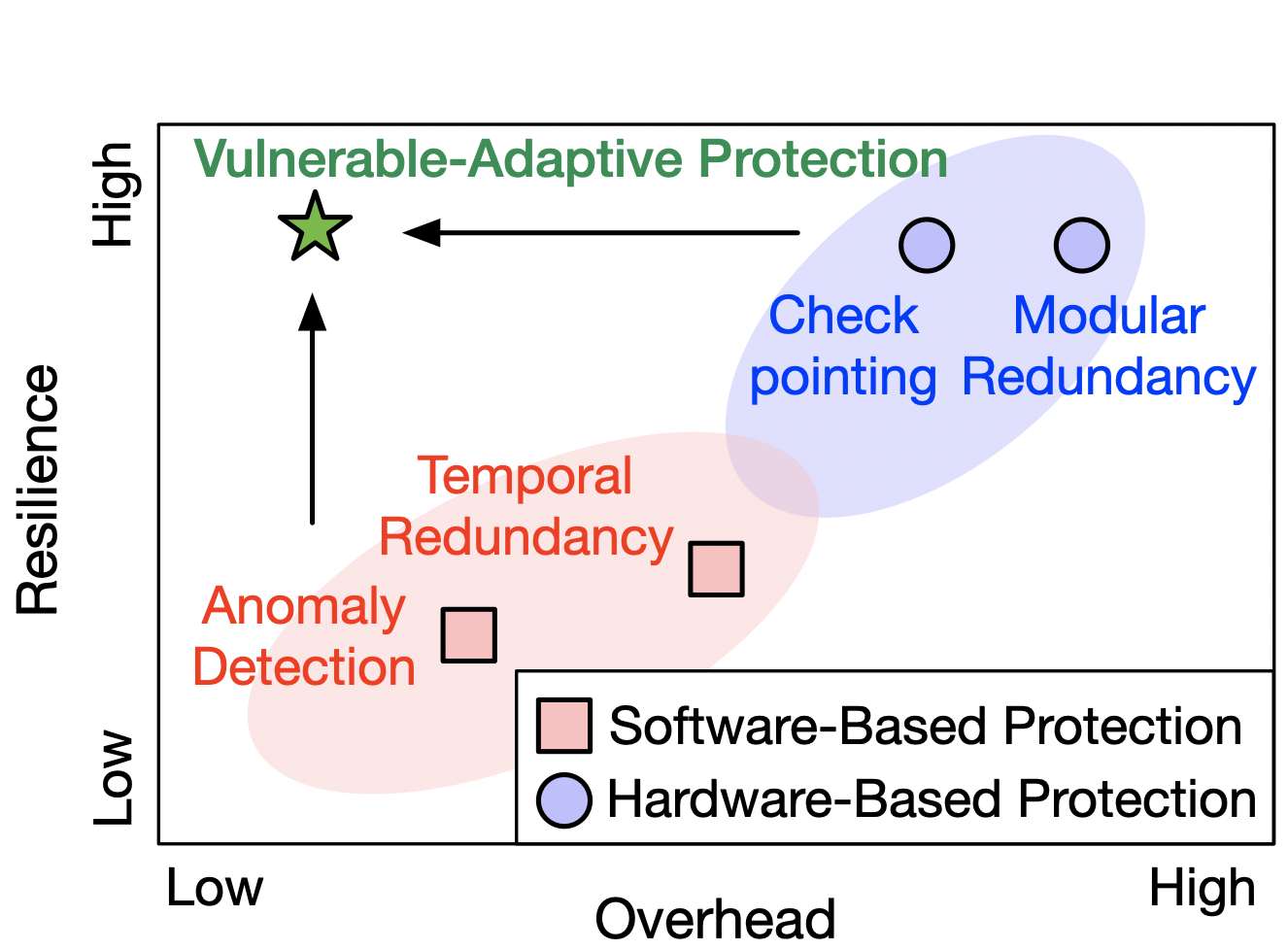

Zishen Wan*, Yiming Gan*, Bo Yu, Shaoshan Liu, Arijit Raychowdhury, Yuhao Zhu Communications of the ACM (CACM), 2024 Paper / Slide / ACM News / GT News / TechXplore News / MIT Technology Review News We characterize the inherent resilience of different compute kernels in autonomous vehicles and drones systems. We analyze the protection design landscape and propose the lightweight Vulnerable-Adaptive Protection (VAP) paradigm for resilient autonomous machines. |

|

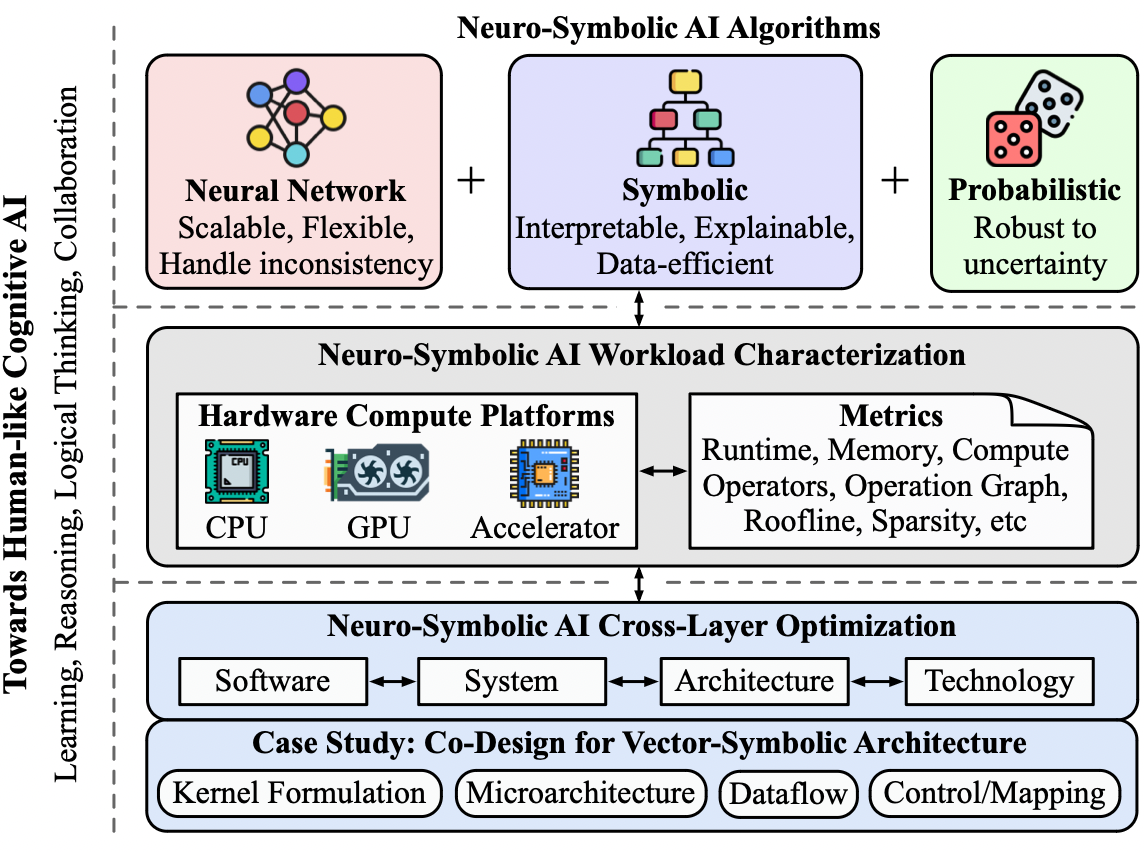

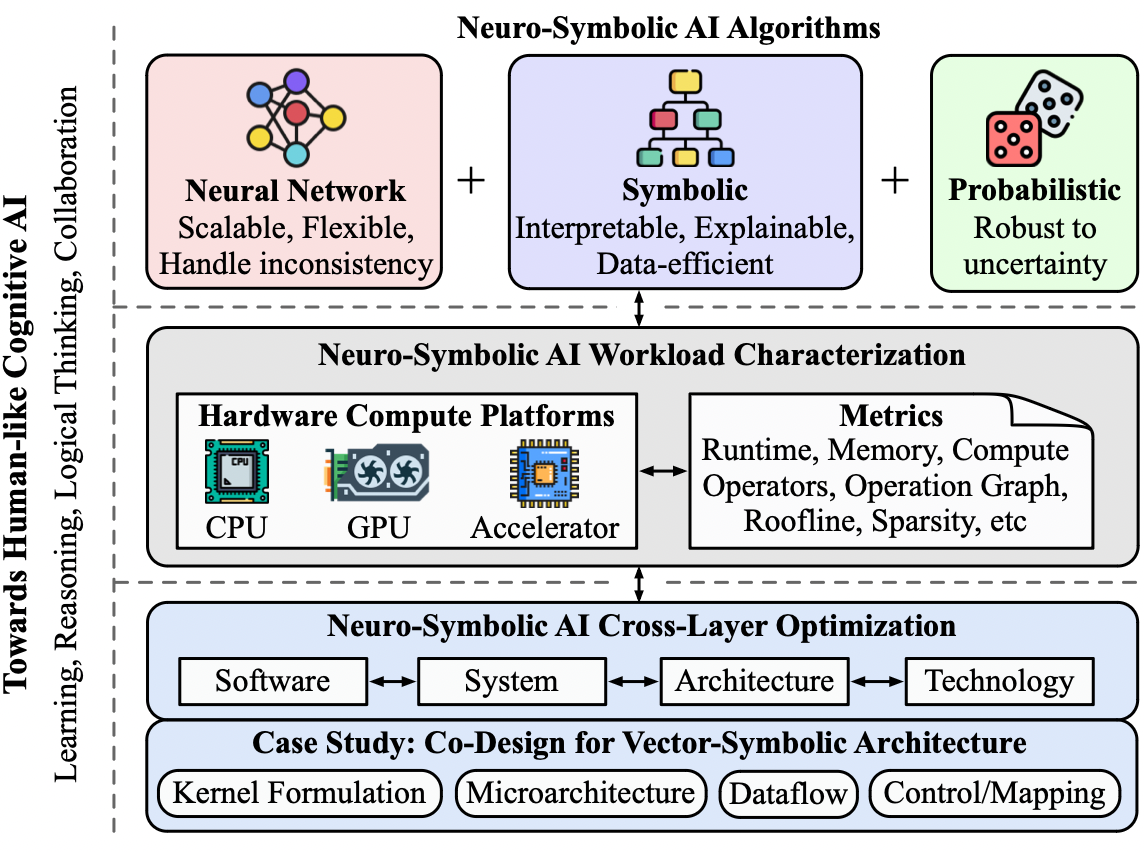

Zishen Wan, Che-Kai Liu, Hanchen Yang, Ritik Raj, Chaojian Li, Haoran You, Yonggan Fu, Cheng Wan, Sixu Li, Youbin Kim, Ananda Samajdar, Yingyan (Celine) Lin, Mohamed Ibrahim, Jan M. Rabaey, Tushar Krishna, Arijit Raychowdhury IEEE Transactions on Circuits and Systems for Artificial Intelligence (TCASAI), 2024 Best Paper Award, DARPA SRC JUMP 2.0, 2024 Top-1 Most Cited Paper in all TCASAI Papers Paper / Fortune News / CoCoSys News We analyze the neuro-symbolic workload chracteristics, and present a hardware acceleration case study for vector-symbolic architecture to improve the performance, efficiency, and scalability of neuro-symbolic computing. |

|

Zishen Wan, Che-Kai Liu, Hanchen Yang, Ritik Raj, Chaojian Li, Haoran You, Yonggan Fu, Cheng Wan, Ananda Samajdar, Yingyan (Celine) Lin, Tushar Krishna, Arijit Raychowdhury IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2024 Best Poster Award, DARPA SRC JUMP2.0 CoCoSys Center 2024 Paper / Slide / Media We systematically categorize neuro-symbolic AI workloads, conduct workload characterizations across hardware platforms, and identify cross-layer optimization opportunites for neuro-symbolic systems. |

|

Zishen Wan, Yuhang Du, Mohamed Ibrahim, Yang (Katie) Zhao, Tushar Krishna, Arijit Raychowdhury ACM/IEEE International Conference on Computer-Aided Design (ICCAD), 2024 Paper We present a cognitive-inspired modular framework for cooperative embodied AI systems and identify the system inherent characteristics and optimization opportunities. Evaluated on long-horizon multi-objective tasks, our cross-layer optimization achieves an average 3.93x speedup in end-to-end task execution. |

|

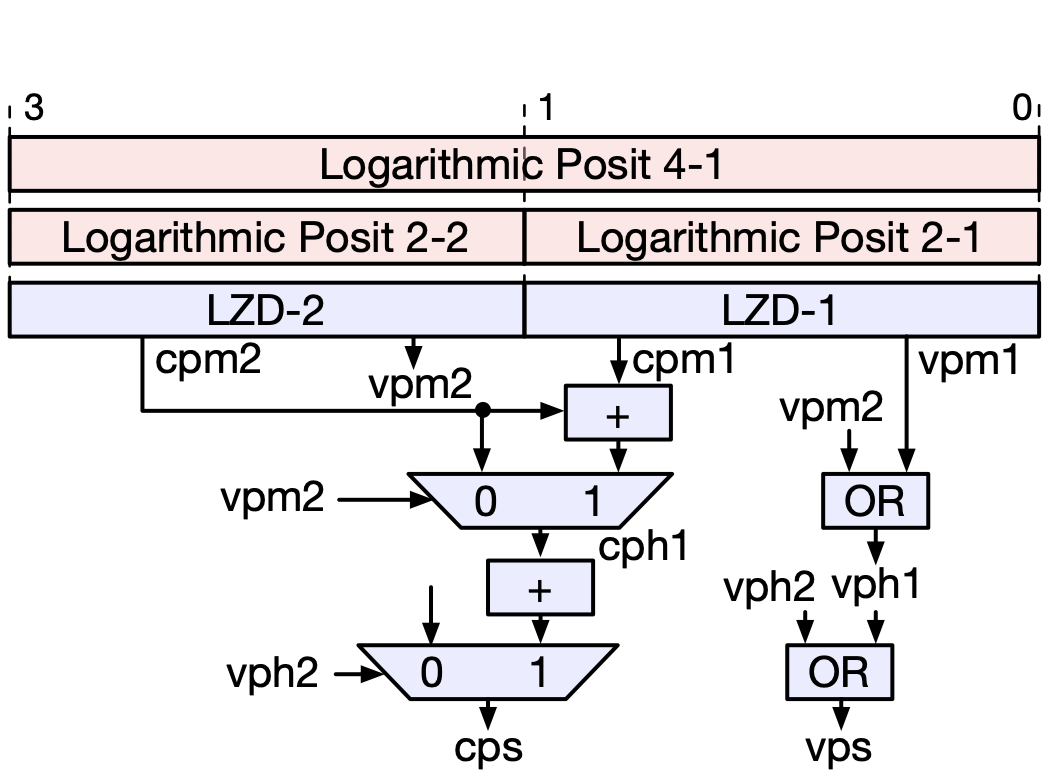

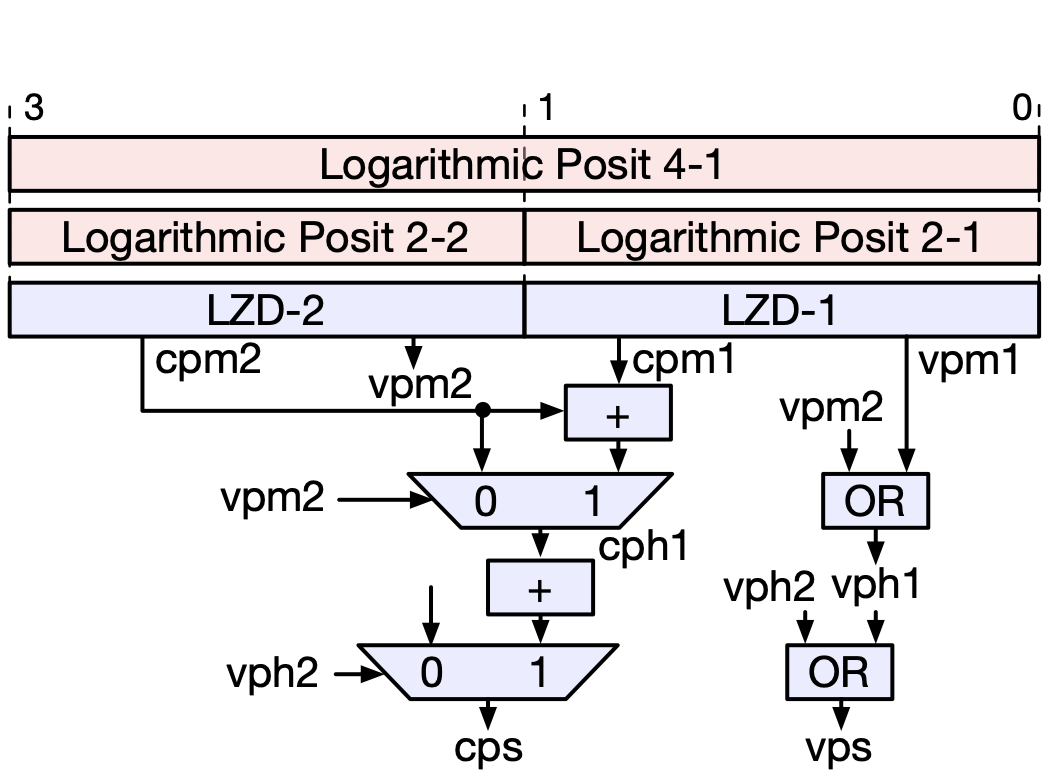

Akshat Ramachandran, Zishen Wan, Geonhwa Jeong, John Gustafson, Tushar Krishna ACM/IEEE Design Automation Conference (DAC), 2024 Paper / Code We present Logarithmic Posit, an adaptive and hardware-friendly datatype that dynamically adapts to DNN weight/activation distributions for efficient inference. We develop Logarithmic Posit quantization and Logarithmic Posit accelerator architecture via algorithm-hardware co-design. |

|

Victor Mayoral-Vilches, Jason Jabbour, Yu-Shun Hsiao, Zishen Wan, Alejandra Martinez-Farina, Martino Crespo-Alvarez, Matthew Stewart, Juan Manuel Reina-Munoz, Prateek Nagras, Gaurav Vikhe, Mohammad Bakhshalipour, Martin Pinzger, Stefan Rass, Smruti Panigrahi, Giulio Corradi, Niladri Roy, Phillip B. Gibbons, Sabrina M. Neuman, Brian Plancher, Vijay Janapa Reddi IEEE International Conference on Robotics and Automation (ICRA), 2024 Best Paper Award, IROS Robotics Benchmarking Workshop 2023 Paper / Poster / Code / Project Page / Media We introduce RobotPerf, a benchmarking suite to evaluate robotics computing performance across a diverse range of hardware platforms. As an open-source initiative, RobotPerf remains committed to evolving with community input to advance the future of hardware-accelerated robotics. |

|

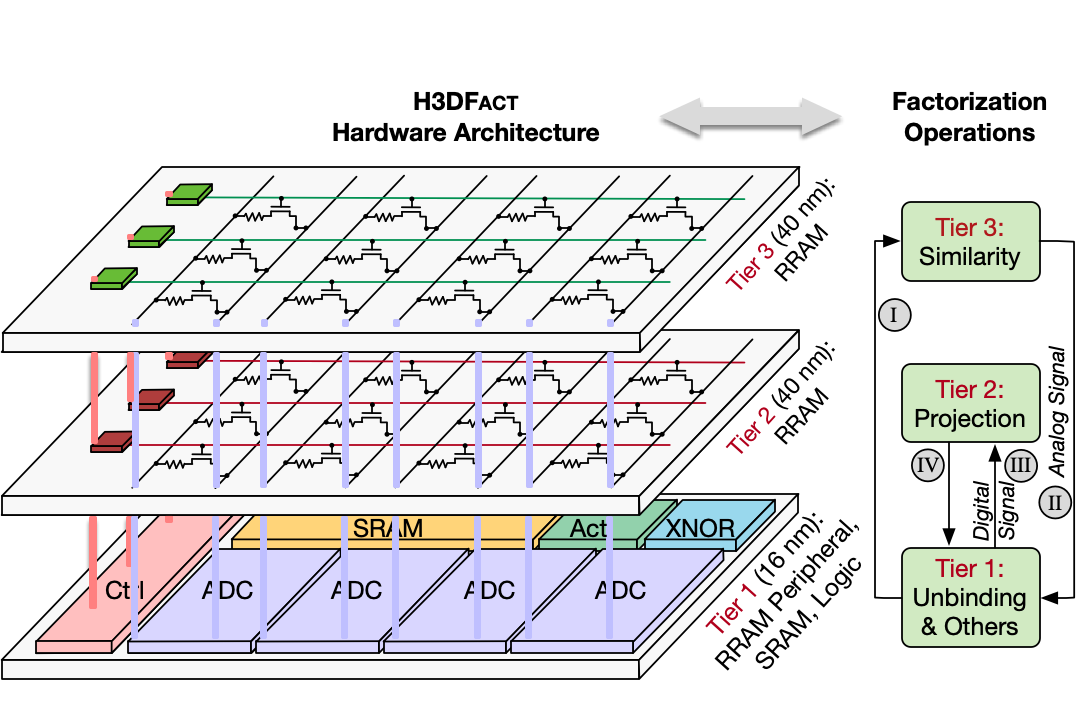

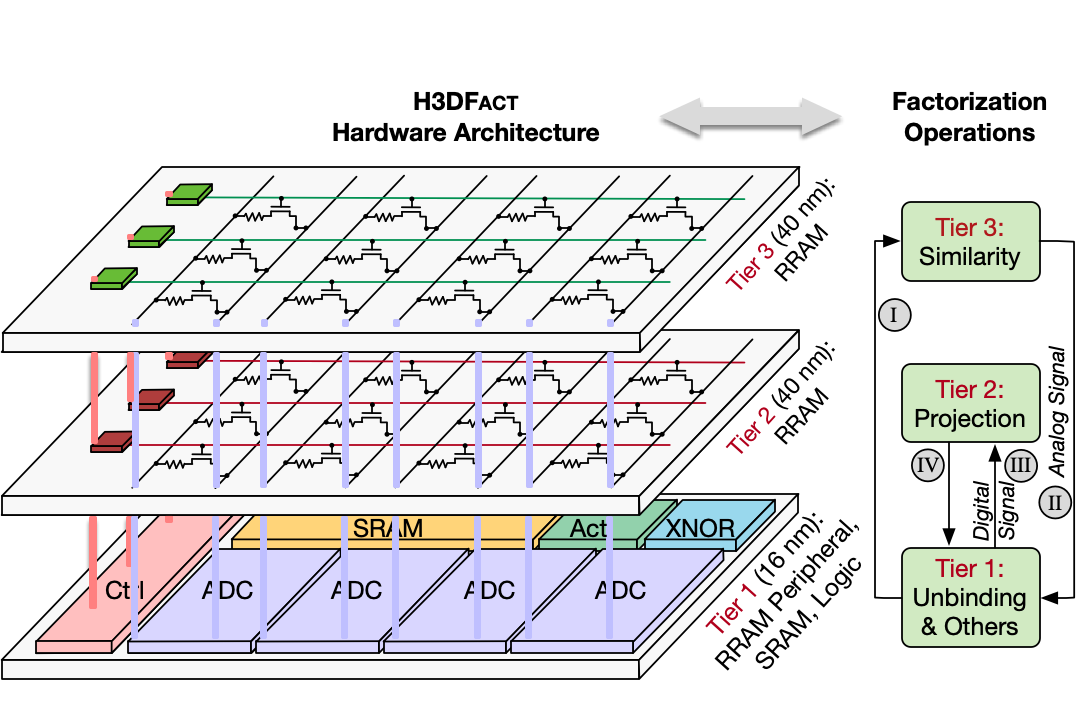

Zishen Wan*, Che-Kai Liu*, Mohamed Ibrahim, Hanchen Yang, Samuel Spetalnick, Tushar Krishna, Arijit Raychowdhury Design, Automation and Test in Europe Conference (DATE), 2024 Best Presentation Award, SRC TECHCON 2024 Paper / Slide / SRC News / GT News We present H3DFACT, the first heterogeneous 3D integrated in-memory compute engine capable of efficiently factorizing high-dimensional holographic representations towards next-generative cognitive AI. |

|

Mohamed Ibrahim, Zishen Wan, Haitong Li, Priyadarshini Panda, Tushar Krishna, Pentti Kanerva, Yiran Chen, Arijit Raychowdhury ACM/IEEE Embedded Systems Week (ESWEEK), 2024 Paper / Slide We analyze the computational challenges of integrating LLMs and neuro-symbolic architecture, and explore state-of-the-art solutions, focusing on the memory-centric computing principles at both algorithmic and hardware levels. |

|

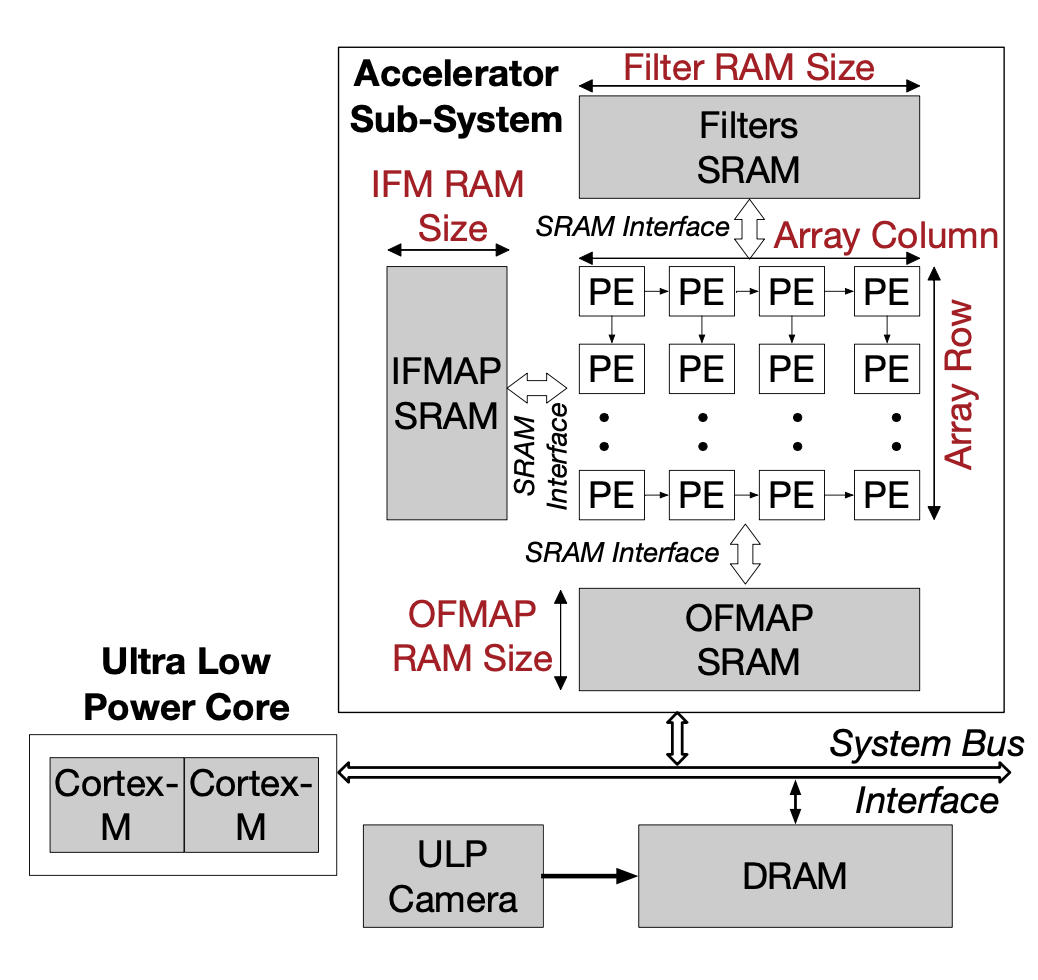

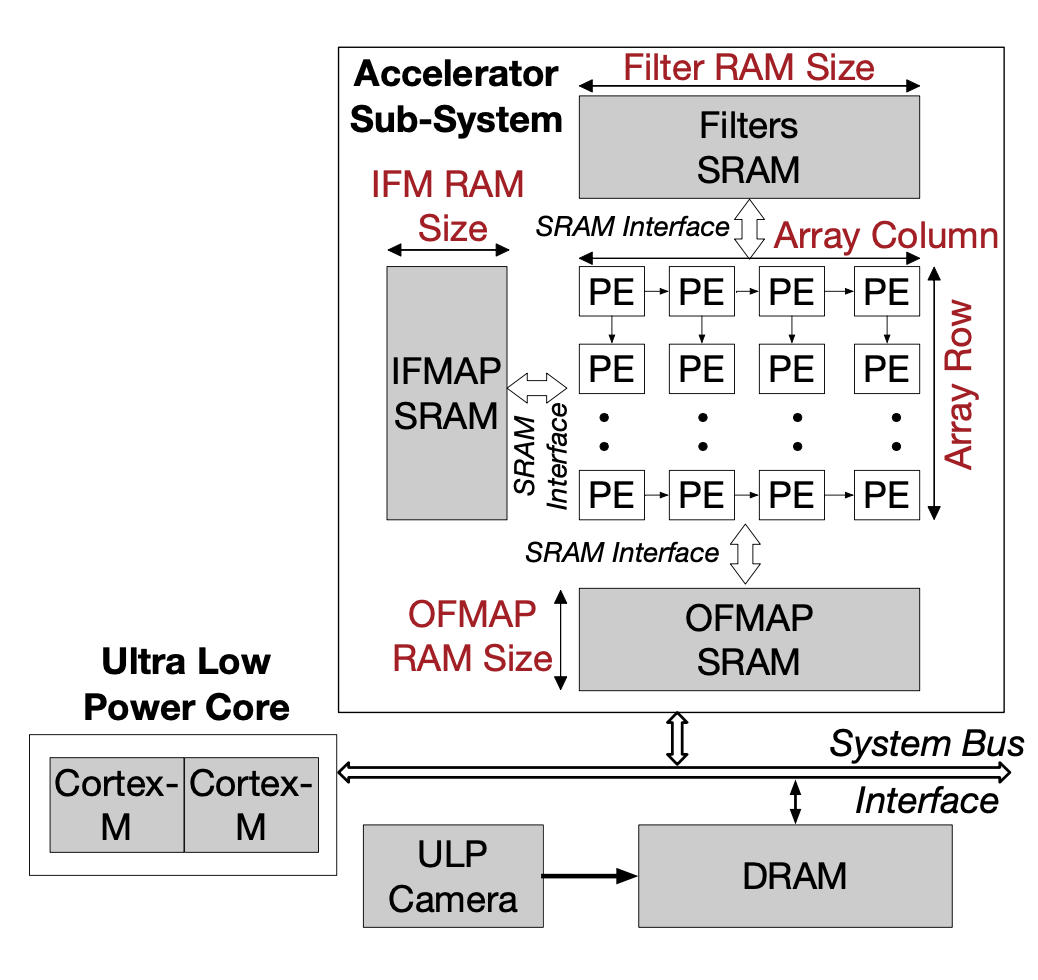

Muya Chang*, Ashwin Lele*, Samuel Spetalnick, Brian Crafton, Shota Konna, Zishen Wan, Ashwin Bhat, Win-San Khwa, Yu-der Chih, Meng-Fan Chang, Arijit Raychowdhury IEEE International Solid-State Circuits Conference (ISSCC), 2023 IEEE Journal of Solid-State Circuits (JSSC), 2023 Paper (ISSCC short version) / Paper (JSSC long version) We propose a fully-programmable heterogeneous ARM Cortex-based SoC with an in-memory low-power RRAM-based CNN and a near-memory high-speed SRAM-based SNN in a hybrid architecture, for high-speed target identification and tracking applications. |

|

Zishen Wan, Nandhini Chandramoorthy, Karthik Swaminathan, Pin-Yu Chen, Vijay Janapa Reddi, Arijit Raychowdhury ACM/IEEE Design Automation Conference (DAC), 2023 Paper / Slide / Poster We propose BERRY, a robust learning framework to improve bit error robustness and energy efficiency for RL autonomous systems. BERRY enables robust low-voltage operation on UAVs, leading to high energy savings in both compute-level operation and system-level quality-of-flight. |

|

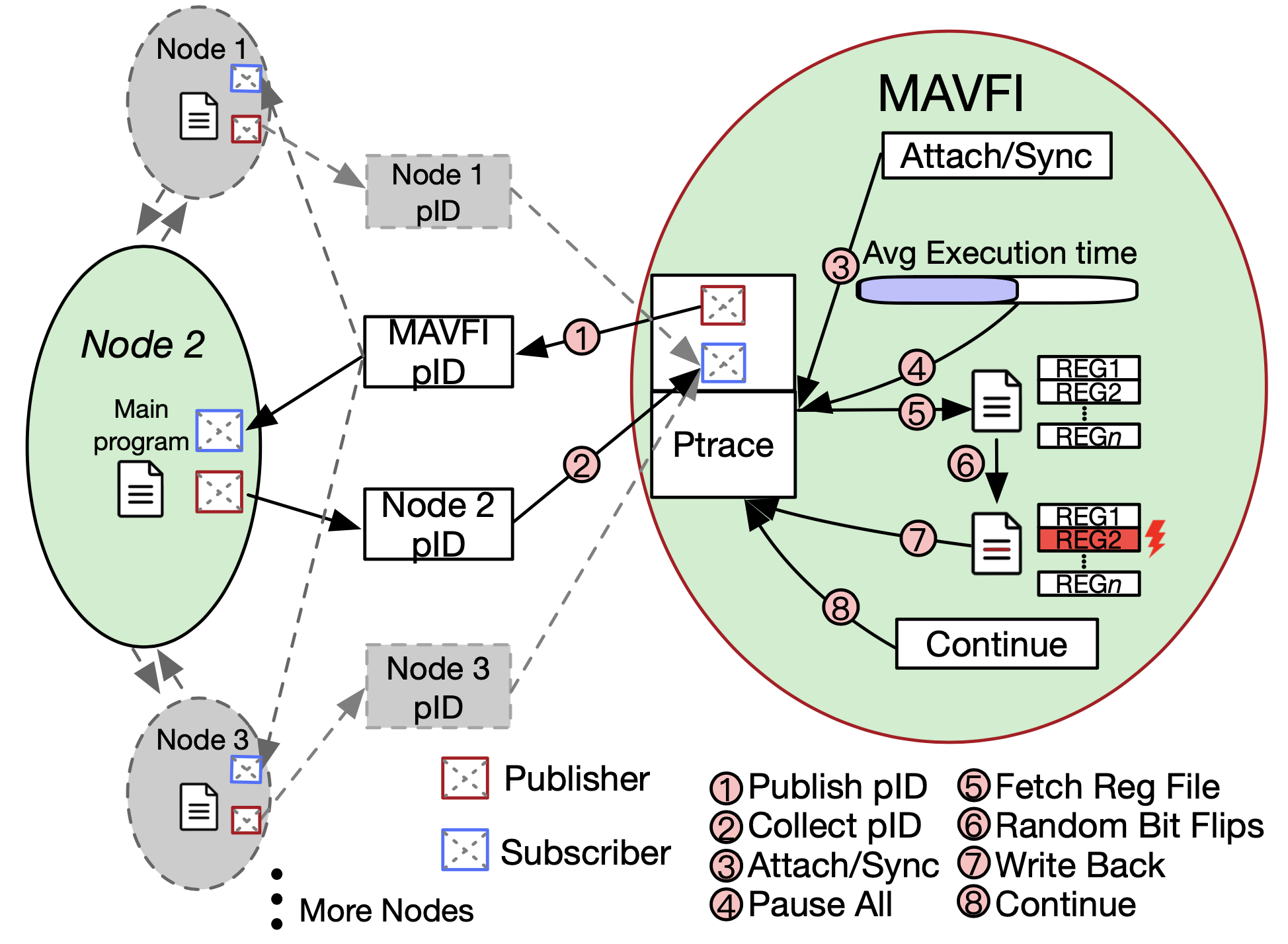

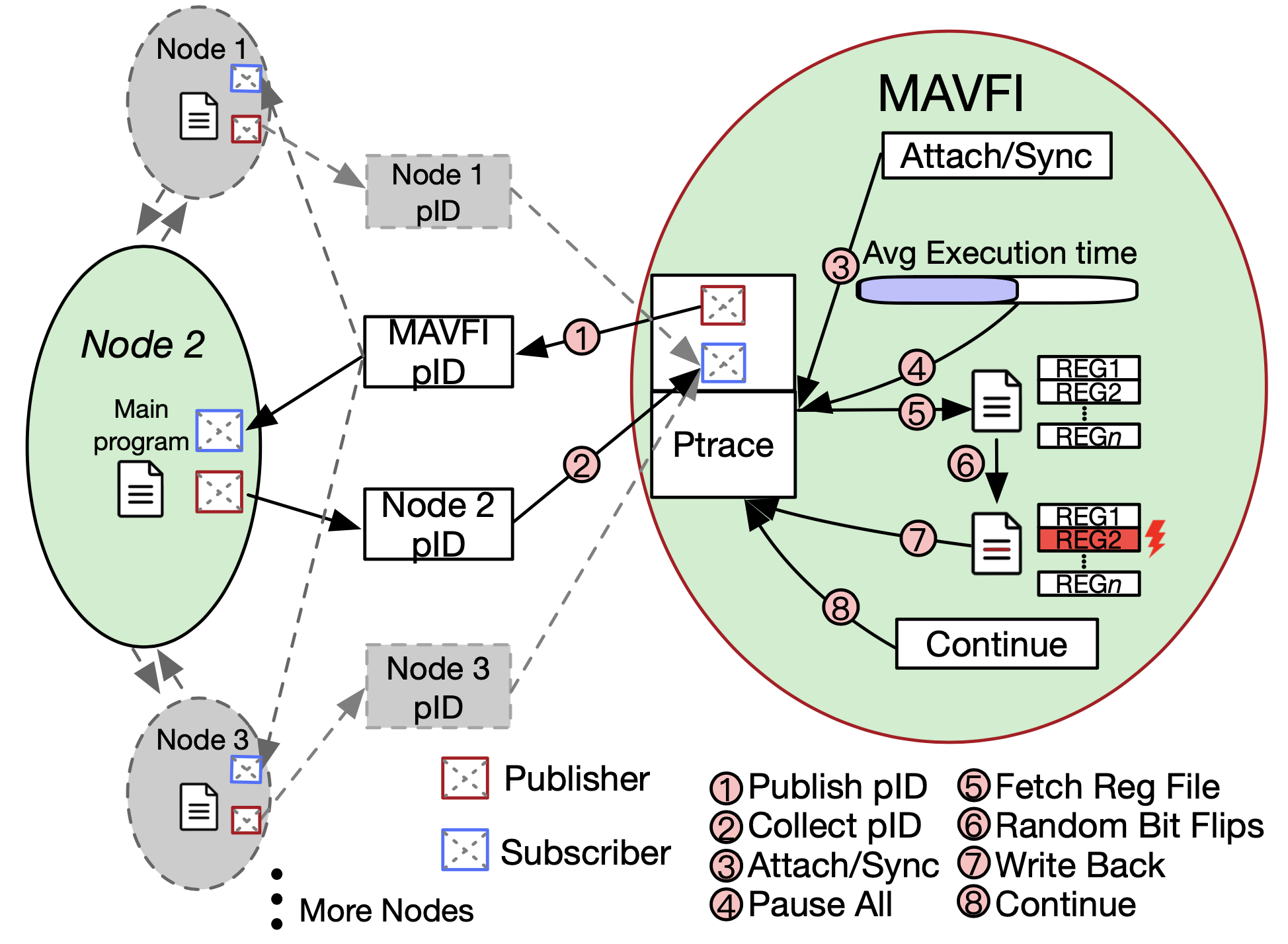

Yu-Shun Hsiao*, Zishen Wan*, Tianyu Jia, Radhika Ghosal, Abdulrahman Mahmoud, Arijit Raychowdhury, David Brooks, Gu-Yeon Wei, Vijay Janapa Reddi Design, Automation and Test in Europe Conference (DATE), 2023 IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2023 Paper (DATE short version) / Paper (TCAD long version) / Slide / Poster / Code We build a ROS-based end-to-end fault analysis framework to understand the resilience of Micro Aerial Vehicles (MAVs) system, and propose two low overhead anomaly-based transient fault detection and recovery schemes. |

|

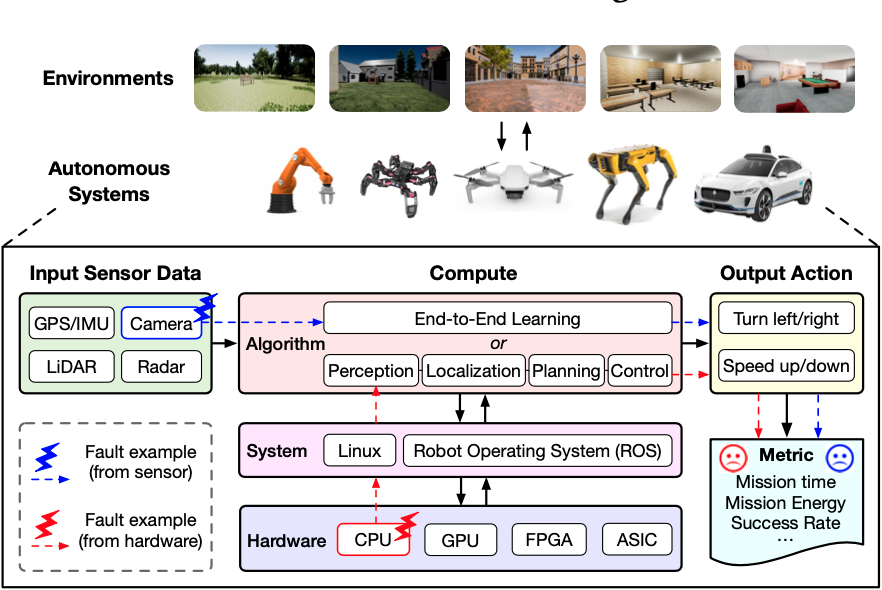

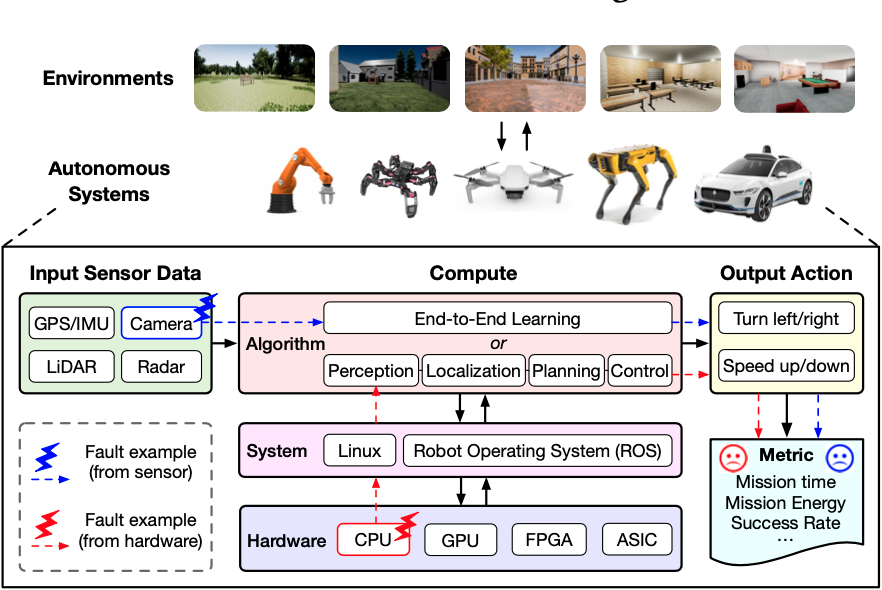

Zishen Wan, Karthik Swaminathan, Pin-Yu Chen, Nandhini Chandramoorthy, Arijit Raychowdhury IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2022 Paper / Media / Blog (in CN) We explore the various origins of fault sources across the computing stack of autonomous systems, and discuss the diverse fault impacts and fault mitigation techniques of different scales of autonomous systems. |

|

Srivatsan Krishnan, Zishen Wan, Kshitij Bhardwaj, Paul Whatmough, Aleksandra Faust, Sabrina M. Neuman, Gu-Yeon Wei, David Brooks, Vijay Janapa Reddi IEEE/ACM International Symposium on Microarchitecture (MICRO), 2022 IEEE Micro Top Picks 2023 Honorable Mention Paper / arXiv We propose a machine learning-based design space exploration framework, Autopilot, that can automate the full system cyber-physical co-design for aerial robots. AutoPilot consistently outperforms general-purpose processors and specialized accelerators built for drones. |

|

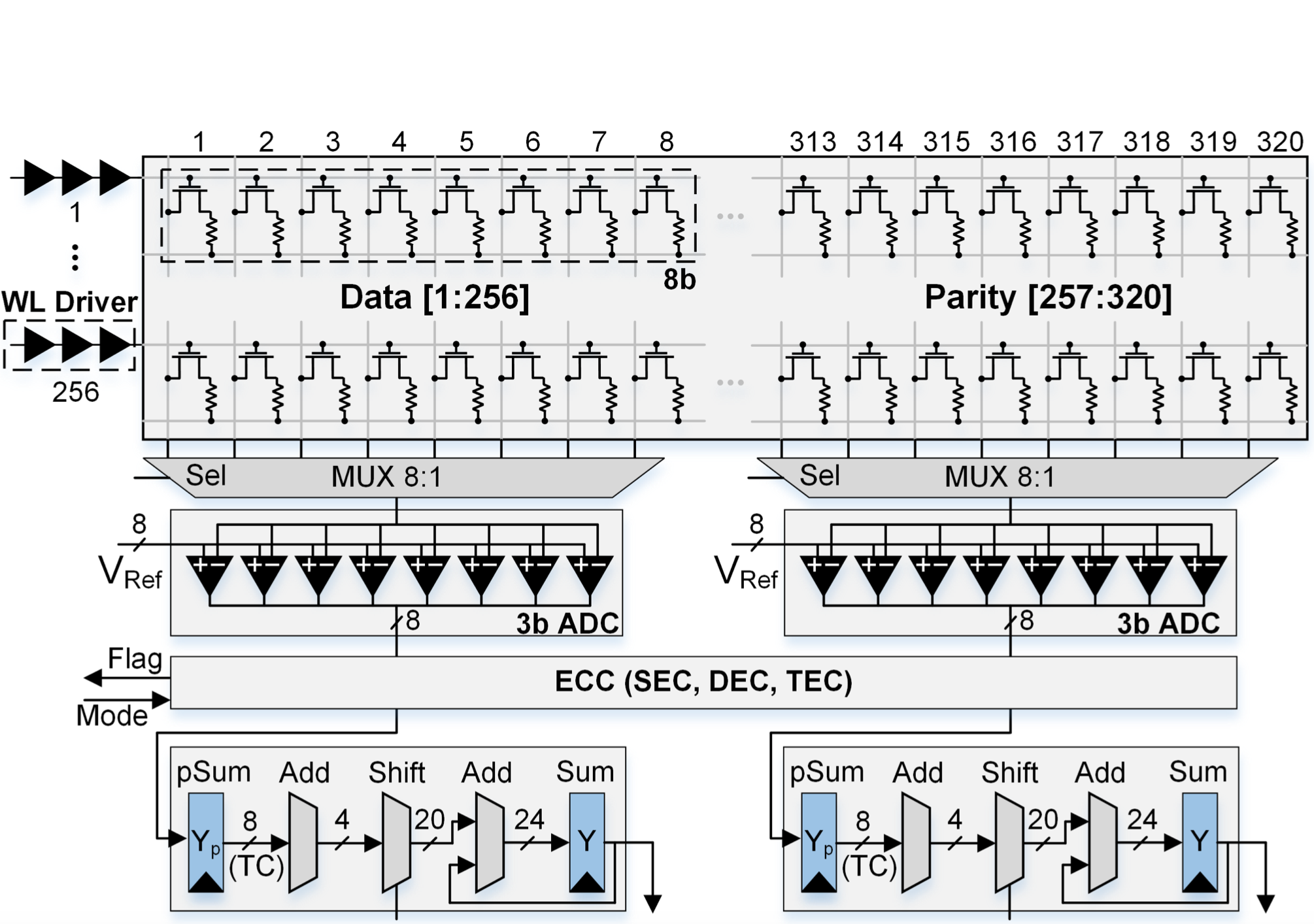

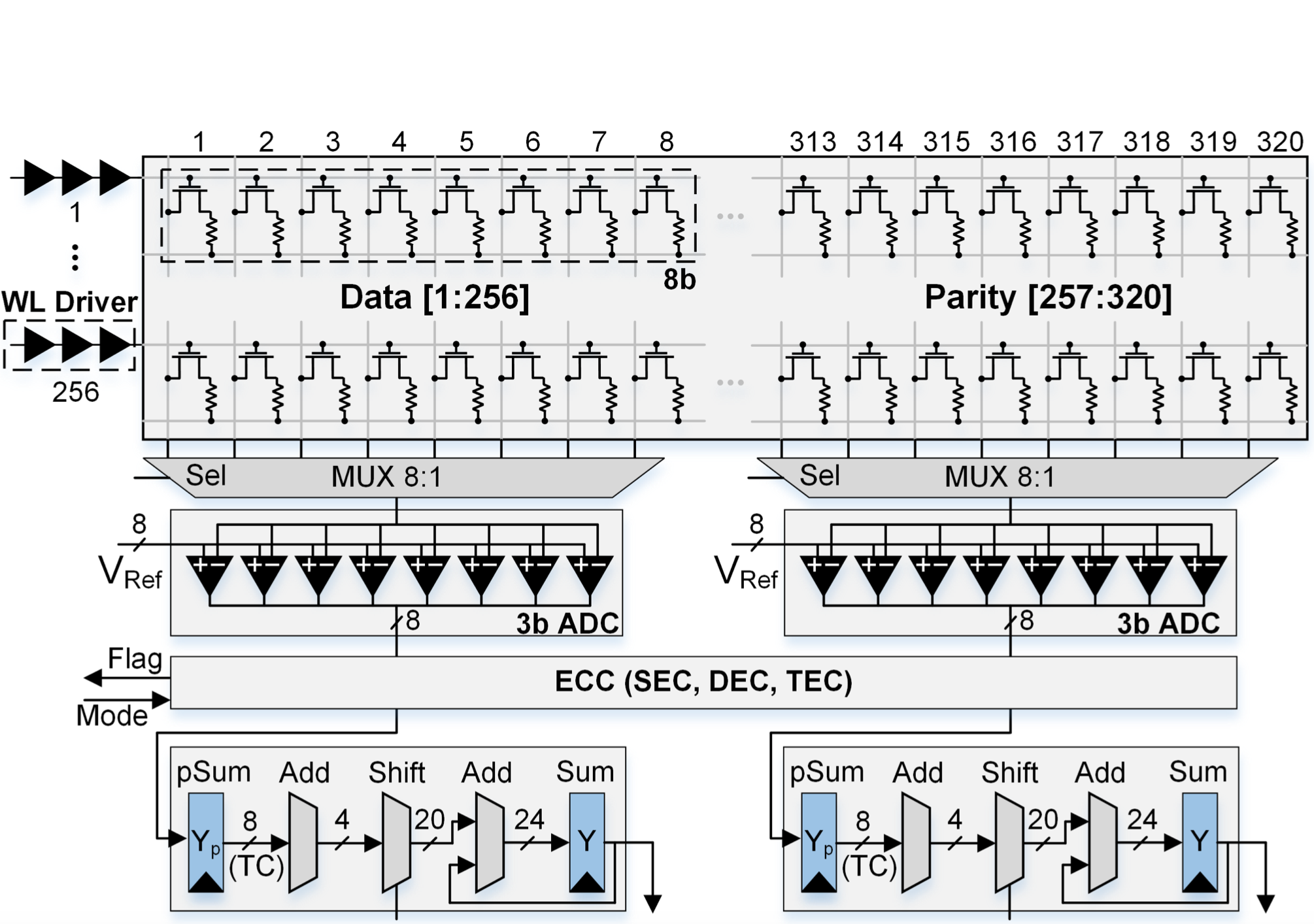

Brian Crafton, Zishen Wan, Samuel Spetalnick, Jong-Hyeok Yoon, Wei Wu, Carlos Tokunaga, Vivek De, Arijit Raychowdhury ACM/IEEE Design Automation Conference (DAC), 2022 Paper / Video / Media We propose a new ECC scheme for hard and soft errors in foundry RRAM-based Compute-In-Memory chip. We demonstrate single, double, and triple error correction offering up to 16,000× reduction in bit error rate, while consuming only 29.1% area and 26.3% power overhead. |

|

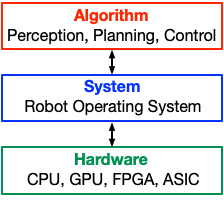

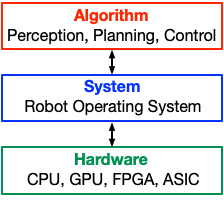

Zishen Wan, Ashwin Lele, Bo Yu, Shaoshan Liu, Yu Wang, Vijay Janapa Reddi, Cong (Callie) Hao, Arijit Raychowdhury IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2022 Paper / Slide / Video We present the cross-layer robotic computing stack, illustrate the current progress and key design techniques. We summarize and highlight the challenges, research opportunities, and roadmap for the next-generation FPGA-based robotic computing systems. |

|

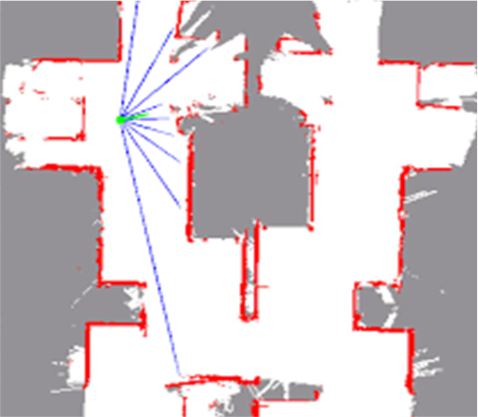

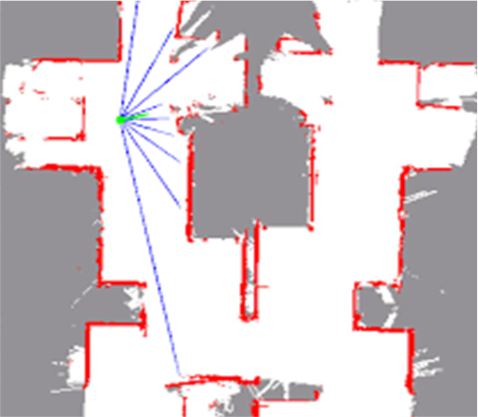

Qiang Liu*, Zishen Wan*, Bo Yu*, Weizhuang Liu, Shaoshan Liu, Arijit Raychowdhury IEEE Custom Integrated Circuits Conference (CICC), 2022 Paper / Slide We present an energy-efficient and runtime-reconfigurable FPGA-based accelerator for robotic localization tasks. We exploit SLAM-specific data locality, sparsity, reuse, and parallelism, and achieve >5x performance improvement over state-of-the-art. |

|

Srivatsan Krishnan, Zishen Wan, Kshitij Bhardwaj, Ninad Jadhav, Aleksandra Faust, Vijay Janapa Reddi IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2022 Paper / Skyline Tool We present a bottleneck analysis tool, Skyline, for designing compute systems for autonomous Unmanned Aerial Vehicles (UAV). The tool provides insights by exploiting the fundamental relationships between various components in the autonomous UAV such as sensor, compute, body dynamics. |

|

Zishen Wan, Aqeel Anwar, Abdulrahman Mahmoud, Tianyu Jia, Yu-Shun Hsiao, Vijay Janapa Reddi, Arijit Raychowdhury Design, Automation and Test in Europe Conference (DATE), 2022 Paper / Slide We characterize the hardware transient fault impact on federated reinforcement learning system, a swarm intelligence paradigm in autonomous machines. We further propose application-aware cost-effective fault detection and mitigation scheme to enable autonomy reliability. |

|

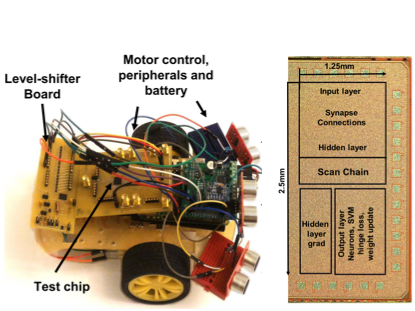

Zishen Wan, Ashwin Lele, Arijit Raychowdhury Asia and South Pacific Design Automation Conference (ASP-DAC), 2022 Paper / Slide We present a series of ultra-low-power accelerator and system designs on enabling the intelligence in edge robotic platforms, with an emphasis on mixed-signal circuit, neuro-inspired computing, benchmarking, software infrastructure, and algorithm-hardware co-design. |

|

Zishen Wan, Aqeel Anwar, Yu-Shun Hsiao, Tianyu Jia, Vijay Janapa Reddi, Arijit Raychowdhury ACM/IEEE Design Automation Conference (DAC), 2021 Best Presentation Award as DAC Young Fellow Paper / Slide / Video / Media We evaluate the resilience of learning-based navigation systems to transient and permanent hardware faults. We further propose two efficient fault mitigation techniques for both RL training and inference. |

|

Zishen Wan*, Bo Yu*, Thomas Yuang Li, Jie Tang, Yuhao Zhu, Yu Wang, Arijit Raychowdhury, Shaoshan Liu IEEE Circuits and Systems Magazine (CAS-M), 2021 Paper We provide an overview of recent work on FPGA-based robotic accelerators. An analysis of software and hardware optimization techniques and main technical issues is presented, along with some commercial and space applications. |

|

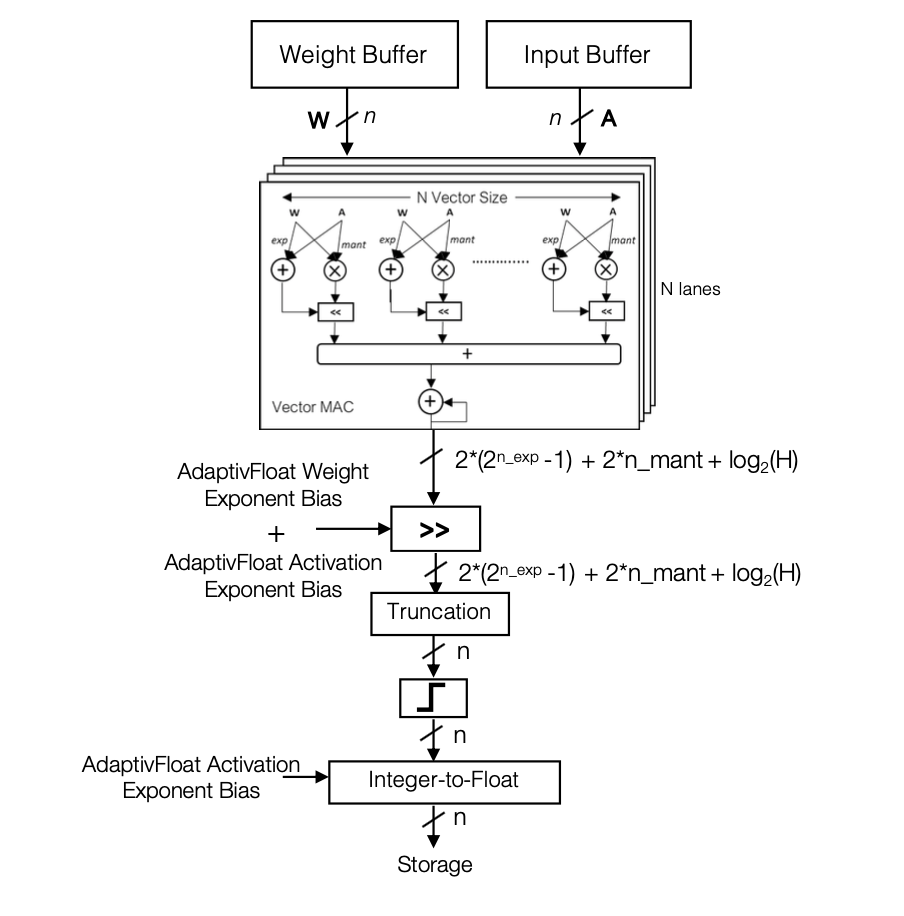

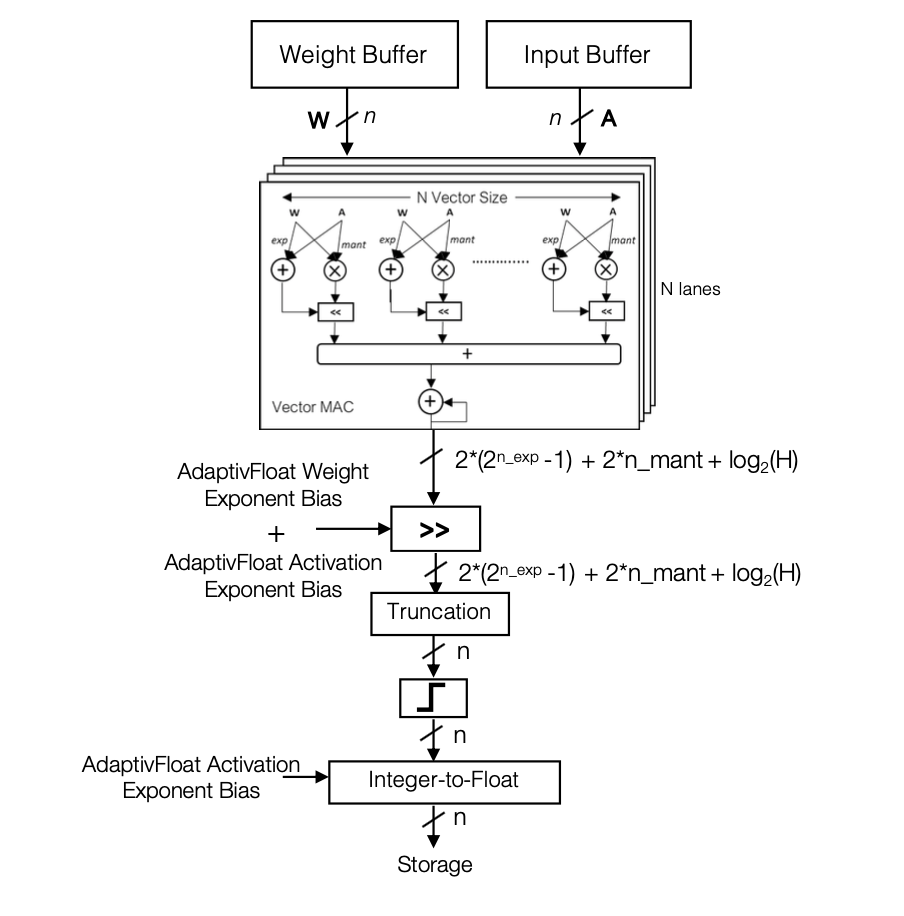

Thierry Tambe, En-Yu Yang, Zishen Wan, Yuntian Deng, Vijay Janapa Reddi, Alexander Rush, David Brooks, Gu-Yeon Wei ACM/IEEE Design Automation Conference (DAC), 2020 Best Paper Award ACM SIGDA Research Highlights Nominee Paper / arXiv (long version) / Media We present an algorithm-hardware co-design centered around a novel floating-point inspired number format, which can achieve higher inference accuracies and lower per-operation energy compared to NVDLA-like PE. |

|

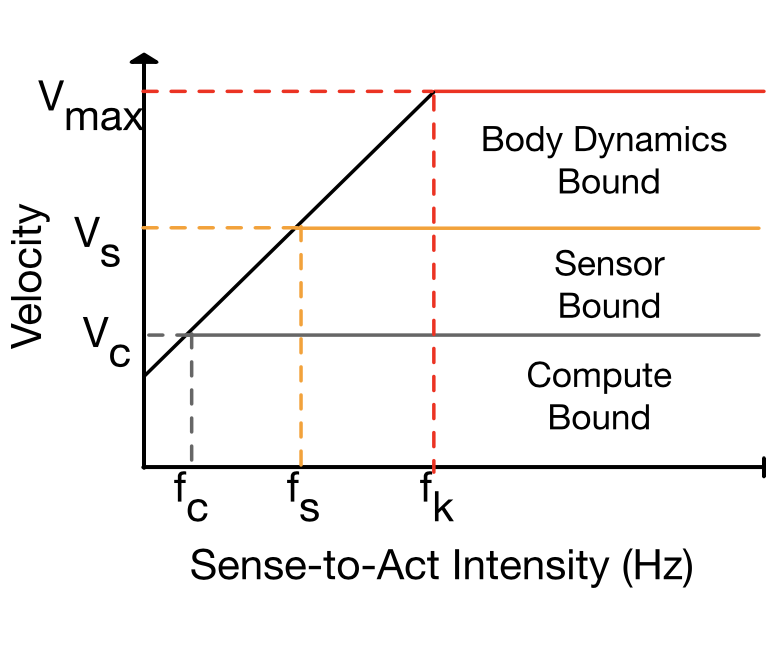

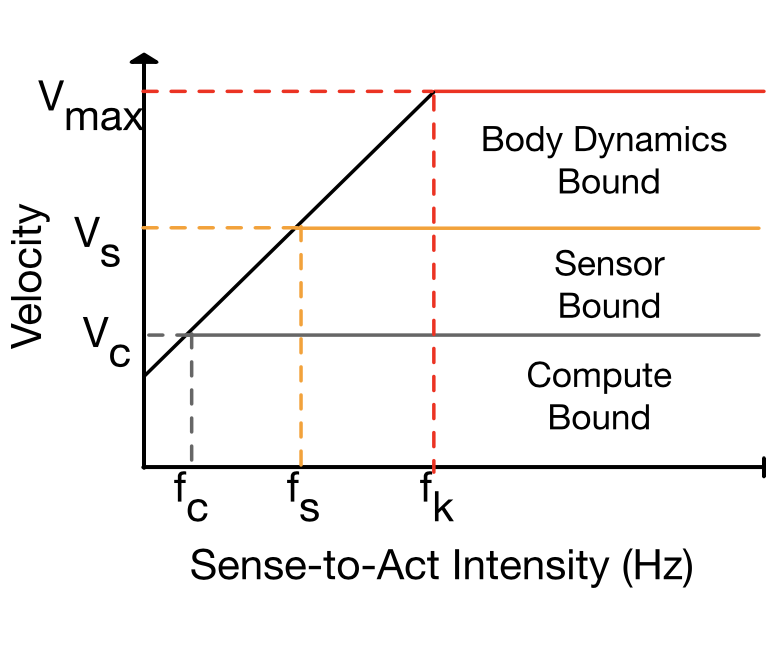

Srivatsan Krishnan, Zishen Wan, Kshitij Bhardwaj, Paul Whatmough, Aleksandra Faust, Gu-Yeon Wei, David Brooks, Vijay Janapa Reddi IEEE Computer Architecture Letters (CAL), 2020 Best Paper Award Invited presentation at International Symposium on High-Performance Computer Architecture (HPCA), 2021 Paper / Tool Website We introduce a roofline-like model to understand the role of computing in aerial autonomous machines. The model provides insights by exploiting the fundamental relationships between various components in an aerial robot, such as sensor framerate, compute performance, and body dynamics. |

|

- 10/2025 MICRO PhD Forum, IEEE/ACM International Symposium on Microarchitecture (MICRO), Seoul, Korea - 06/2025 DAC PhD Forum, IEEE/ACM Chips to Systems Conference (DAC), San Francisco, CA - 06/2025 Invited Talk, ISCA Workshop on Architecture Support for Embodied AI Systems, Online - 03/2025 CoCoSys (Center for the Co-Design of Cognitive Systems) Annual Summit, DARPA SRC JUMP 2.0, Atlanta, GA - 02/2025 Invited Talk, UIUC Coordinated Science Laboratory (CSL), Champaign, IL - 01/2025 Seminar Talk, University of Washington (Host: Prof. Ang Li), Seattle, WA - 12/2024 Seminar Talk, Institute of Computing Technology, Chinese Academy of Sciences (Host: Prof. Yunji Chen), Online - 07/2025 Seminar Talk, University of Notre Dame (Host: Prof. Ningyuan Cao), South Bend, IN - 04/2025 Google (Host: Dr. Suvinay Subramanian), Online - 03/2025 CoCoSys (Center for the Co-Design of Cognitive Systems) Annual Summit, DARPA SRC JUMP 2.0, Atlanta, GA - 01/2025 Guest Lecture, Georgia Tech ECE8893 Parallel Programming for FPGAs (Host: Prof. Callie Hao), Atlanta, GA - 01/2025 Georgia Tech Computer Architecture Research Seminar (Arch-Whisky), Atlanta, GA - 11/2024 ACM Student Research Competition, International Symposium on Microarchitecture (MICRO), Austin, TX - 08/2024 Invited Talk, University of Minnesota, Twin Cities (Host: Prof. Katie Zhao), Minneapolis, MN - 05/2024 Young Professional Symposium, Conference on Machine Learning and Systems (MLSys), Santa Clara, CA - 05/2024 International Workshop on Neuro-symbolic Systems (NeuS), UC Berkeley, Berkeley, CA - 03/2024 CoCoSys (Center for the Co-Design of Cognitive Systems) Annual Summit, DARPA SRC JUMP 2.0, Atlanta, GA - 09/2023 Guest Lecture, EE6900 Neuromorphic Computing (Host: Prof. Yan Fang), Atlanta, GA - 05/2023 Georgia Tech 3D Systems Packaging Research Center Spring Meeting, Atlanta, GA - 05/2023 CoCoSys (Center for the Co-Design of Cognitive Systems) Annual Summit, DARPA SRC JUMP 2.0, Atlanta, GA - 08/2024 Invited Talk, Lawrence Livermore National Laboratory (Host: Dr. Kshitij Bhardwaj), Livermore, CA - 11/2024 Invited Talk, MICRO Workshop on Robotics Acceleration with Computing Hardware, Austin, TX - 09/2024 ESWEEK (Embedded Systems Week) PhD Forum, Raleigh, NC - 05/2024 Cyber-Physical System Rising Star Workshop, University of Virginia, Charlottesville, VA - 05/2024 CoCoSys (Center for the Co-Design of Cognitive Systems) Liaison Meeting, DARPA SRC JUMP 2.0, Atlanta, GA - 02/2024 CRIDC (Career, Research, and Innovation Development Conference), Atlanta, GA - 02/2024 Georgia Tech Computer Architecture Research Seminar (Arch-Whisky), Atlanta, GA - 11/2023 6th IBM AI Compute Symposium, IBM T.J. Watson Research Center, Yorktown Heights, NY - 08/2023 ML and Systems Rising Stars Workshop, Google, Mountain View, CA - 05/2023 Georgia Tech Chips Day, Atlanta, GA - 03/2023 Georgia Tech EIC Lab (Host: Prof. Celine Lin), Atlanta, GA - 02/2023 CRNCH (Center for Research into Novel Computing Hierarchies) Annual Summit, Atlanta, GA - 11/2022 ACM Student Research Competition at ICCAD, San Diego, CA - 02/2023 CRIDC (Career, Research, and Innovation Development Conference), Atlanta, GA - 10/2022 5th IBM AI Compute Symposium, IBM T.J. Watson Research Center, Yorktown Heights, NY - 10/2022 CBRIC (Research Center for Brain-Inspired Computing) Annual Summit, DARPA JUMP SRC, Purdue University, IN - 03/2022 Guest Lecture, Georgia Tech ECE8893 Parallel Programming for FPGAs (Host: Prof. Callie Hao), Atlanta, GA - 02/2022 CRNCH (Center for Research into Novel Computing Hierarchies) Annual Summit, Online - 02/2024 CRNCH (Center for Research into Novel Computing Hierarchies) Annual Summit, Atlanta, GA - 05/2023 CoCoSys (Center for the Co-Design of Cognitive Systems) Annual Summit, DARPA SRC JUMP 2.0, Atlanta, GA - 11/2022 ACM Student Research Competition at ESWEEK, Online - 06/2022 COMPSAC plenary panel 'Reliability of Autonomous Machines', Online - 10/2021 CBRIC (Center for Brain-Inspired Computing) Annual Summit, DARPA JUMP SRC, Online - 08/2021 CBRIC (Center for Brain-Inspired Computing) Industry Talk, DARPA JUMP SRC, Online - 07/2020 Harvard Architecture, Circuits and Compilers Lab, Online |

- ECE8803 SW-HW Co-Design for ML Systems, Georgia Tech, Spring 2025, "Opportunities and Challenges for In-/Near-memory Computing" - ECE8893 Parallel Programming for FPGAs, Georgia Tech, Spring 2023, "FPGA-based Robotic Computing" - ECE8893 Parallel Programming for FPGAs, Georgia Tech, Spring 2022, "FPGA-based Robotic Computing" |

|

|

|

|

Last Update: Feb. 2026

|